- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

The example spifi source code from mcu-boot initializes the spifi clock speed to 24MHz. Is this NXP's recommendation for the spifi clock speed for spifi flash in LPC54S018J4M? I was wondering if a higher clock rate would be safe to use. Please advise.

已解决! 转到解答。

Hi,

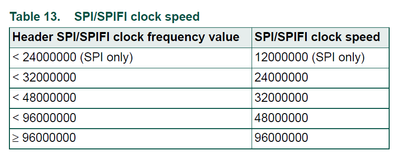

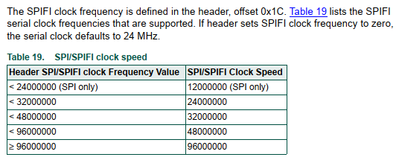

We can refer this table for spifi clock speed setting. The default IMG_BAUDRATE is 0 which means SPIFI clock speed is 24000000. In source code, when set IMG_BAUDRATE as 96000000 or bigger, SPIFI clock speed is 96000000.

So if you want to change SPIFI clock with IMG_BAUDRATE, the maximal clock value is 96000000. The limitation is due to ROM code use internal FRO as clock source.

If you want to get higher SPIFI clock, for example 100MHz, an external clock source and PLL configuration are needed. You can configure SPIFI clock source and divider in source code to get higher SPIFI clock.

Have a nice day,

Jun Zhang

Hi Jun,

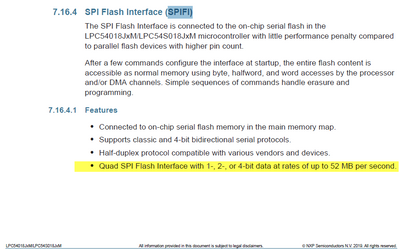

Thank you for responding. 52MB/s data rate is not the same as the clock frequency, as it could take into account 4-bit data. Could you advise what the highest allowed clock frequency should be for spifi flash?

Rex

Hi

According to UM

Transfer rates of up to SPIFI_CLK/2 bytes per second. This is for 4bit data.

According DS,

Quad SPI Flash Interface with 1-, 2-, or 4-bit data at rates of up to 52 MB per second. the maximal 52MB is for 4bit data

So we can say maximal SPIFI_CLK is 104MHz.

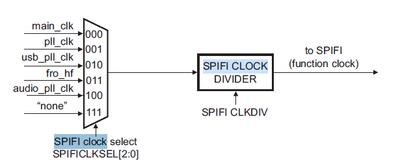

Here is SPIFI clock source

If you choose internal FRO96,

for 4bit data, maximal rate is 96/2=48MB,

For 1bit data, maximal rate is 96/8=12MB

to get 52MB maximal rate, you need use external clock and configure PLL to reach 104M SPIFI_CLK.

Have a nice day,

Jun Zhang

Jun,

Thank you for the clarification. Looking at the XIP project examples in LPC54S018J4M's SDK, it looks like all example XIP projects specify a baud rate of 24MHz by not defining IMG_BAUDRATE.

From the UM:

From the startup file:

#ifdef IMG_BAUDRATE

.long IMG_BAUDRATE /* (0x1C) image baudrate */

#else

.long 0 /* (0x1C) reserved */

#endif

Is this indicative of some issue if the baudrate were set higher?

Also, is it possible for NXP to use a different flash part within LPC54S018J4M such that a higher baudrate might not work?

Rex

Hi,

We can refer this table for spifi clock speed setting. The default IMG_BAUDRATE is 0 which means SPIFI clock speed is 24000000. In source code, when set IMG_BAUDRATE as 96000000 or bigger, SPIFI clock speed is 96000000.

So if you want to change SPIFI clock with IMG_BAUDRATE, the maximal clock value is 96000000. The limitation is due to ROM code use internal FRO as clock source.

If you want to get higher SPIFI clock, for example 100MHz, an external clock source and PLL configuration are needed. You can configure SPIFI clock source and divider in source code to get higher SPIFI clock.

Have a nice day,

Jun Zhang