- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC54S018J - Unable to boot on internal SPIFI with XIP activated on custom board

LPC54S018J - Unable to boot on internal SPIFI with XIP activated on custom board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC54S018J - Unable to boot on internal SPIFI with XIP activated on custom board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am trying to use XIP feature on a custom board without success. The SDK demo "hello_world_qspi_xip" works fine on NXP LCP54S018M-EVK but the same binary is not booting on my board.

My board is working when copying flash to SRAMX then executing code from SRAMX.

Q1: The datasheet mentions that ISP1/2/3 pins (PIO0_4/PIO0_5/PIO0_6) are floating, but on NXP EVK they seems to be pulled-up, even if I can not see any pull-up in the schematic. Why ?

Unfortunately on my board those pins are not connected, so I guess that the boot mode is undetermined and I tried to set BOOT_SRC fuses to SPIFI until we respin the board: it did not work neither.

Q2: OTP writing was an issue on my side, fixed

Q3: Datasheet states that pins N7 and C4 should be connected to enable flash and reset state is "Pulled up" (table 4), but there is a 100 k pull-up in NXP EVK. Why ?

Thank you for your help

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Oliv

Seems, that I have the same problem why I raised the following ticket:

XIP, program not starting on LPC54018J4M custom bo... - NXP Community

Can you tell me the solution for your problem because i may help me?

Thanks

regards

Ron

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Oliv,

Regarding your question, you said your board was working when copying flash to SRAMX then executing code from SRAMX, do you mean that your board can run after Reset even power off/on? I assume that you have downloaded application code to SPIFI flash. If it is the case, I think the boot process is okay.

The only difference between the XIP and SRAM executing is the XIP bit setting for image type(__imghdr_imagetype variable in *.ld file).

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your answer @xiangjun_rong

Yes, when executing from SRAMX the board can run even after a power off/on, so storing data in flash is working

I already checked that bit in the header and it is correctly configured:

Address 0x160 contains (little endian) a5a5 edfe 0300 0000 0000 0010 0439 0000 =>

Header_marker: 0xFEED A5A5

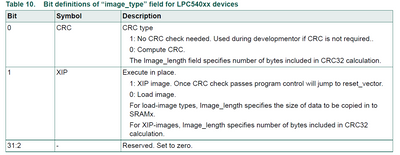

image_type: 0x0000 0003 (No CRC computation, XIP image)

load_adress: 0x1000 0000 (SPIFI XIP)

Image_length: 0x0000 3904

So, if that bit is correctly set and the boot process is correct when booting from SRAM: why NXP SDK board is booting in XIP mode but not mine ? Could we have any race condition between peripherals, like clock startup time ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @xiangjun_rong ,

It seems that all my boards are not having the same behavior: most of them are unable to boot when I use XIP with "BootClockFROHF96M" clock but using "BootClockPLL180M" works with "led_blinky" example. Then I tried to use "QSPI_DELAY" fuse set to 220 ms (0x7). Some of them are able to boot "led_blinky with the FROHF96M clock but I usually get this pattern:

- Boot OK from PLL and FRO clocks everytime with "led_blinky" compiled to use XIP

- Boot OK from PLL with "hello_world_qspi_xip" but not BootClockFROHF96M

- Boot KO with "utick_wakeup_xip" for both clock sources

As the exact same binary is booting on the NXP EVK I guess that I have an hardware issue, any hint on usual suspects?

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Oliv,

Regarding your issue that boot fails with BootClockFROHF96M for some examples, frankly speaking, I have not ideas, probably it is a signal integrity issue for the PCB.

For the "QSPI_DELAY" fuse option, can you tell us where you set it?

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

QSPI_DELAY is from the UM11155 chapter "45.12.4.3 OTP memory bank 3, word 0 - Boot ROM control data", table 1107. Bits 19:17

Regarding free running oscillator it is inside the chip so I am not sure to understand how PCB signal integrity will impact it. I checked the power-supplies with an oscilloscope and they seems to be correct

Thank you

Olivier

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Oliv,

I mean the SPI_CLK_FREQ variable, which is integrated in the image, it determines the SPIFI clock frequency.

Pls refer to an12122.pdf, located at:

https://www.nxp.com.cn/docs/en/application-note/AN12122.pdf

Hope it can help you

BR

XiangJun Rong