- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: System Bus and FlexBus clocks on K64

System Bus and FlexBus clocks on K64

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi all, this question is for a Kinetis MK64FN1M0VLQ12.

I am trying to determine what the FlexBus clock is set to on the MK64FN1M0VLQ12 we use in our product.

It looks like by default, the FlexBus (FB_CLK) is clock is set to be the same as the system bus clock. The core clock runs at 120 Mhz and the bus clock divider is 2 which makes the bus clock 60 Mhz. In terms of the FlexBus clock, I see this in the K64 Sub-Family Reference Manual for the OUTDIV3 field of the SIM_CLKDIV1 register:

Clock 3 output divider value

This field sets the divide value for the FlexBus clock (external pin FB_CLK) from MCGOUTCLK. At the

end of reset, it is loaded with either 0001 or 1111 depending on FTFE _FOPT[LPBOOT]]. The FlexBus

clock frequency must be an integer divide of the system clock frequency.

0000 Divide-by-1.

0001 Divide-by-2.

I can't seem to find any code in our project that sets this value so I assume it is getting the default value of 2 (or maybe I just haven't found the code yet, it is difficult to follow through all the different layers in KSDK v1.3).

Application Note AN4393 says:

FlexBus clock FB_CLK runs at the same speed as the Bus clock. The FB_CLK frequency may be the same as the

internal system bus frequency or an integer divider of that frequency.

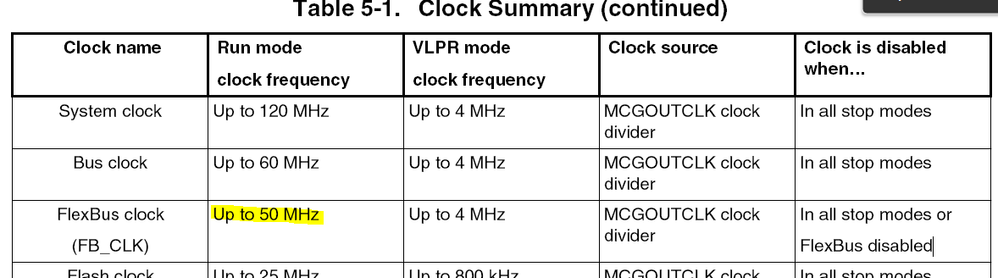

I also see this in the K64 Sub-Family Reference Manual:

If my assumptions are correct and we are setting the FlexBus clock to 60 Mhz, does it actually run at 60 Mhz or does the chip limit it to 50 Mhz internally?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Andrew

The bus speeds are set in the register SIM_CLKDIV1, which is usually performed before setting the PLL to its operating speed in order to ensure not overclocking any of the buses (for example, overclocking the flash bus will cause immediate failure).

It is the responsibility of the code to keep to limits - the chip won't limit and an incorrect clock may cause malfunction if actually used.

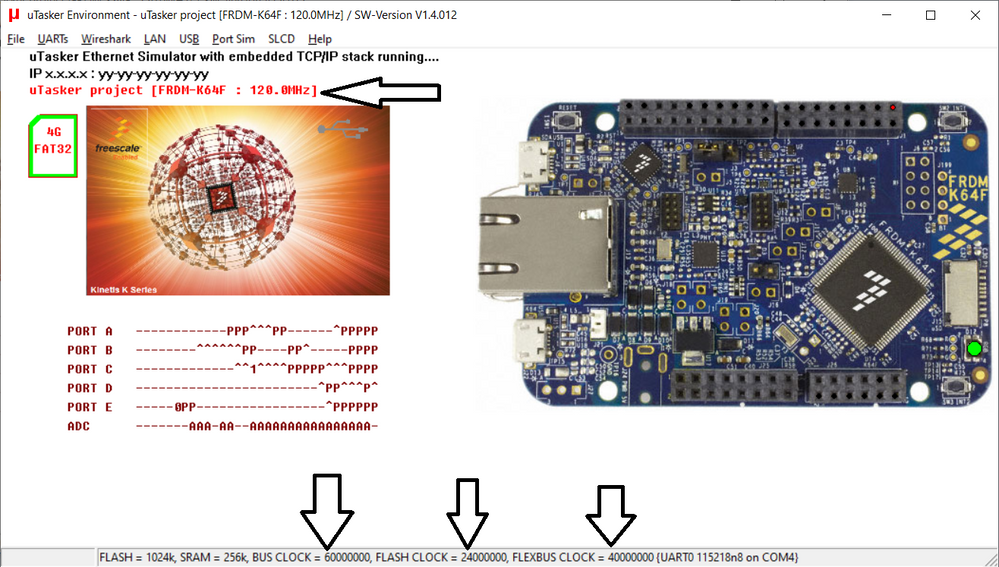

SIM_CLKDIV1 = 0x01240000; for example (with 120MHz PLL output) gives 120MHz core, 60MHz bus, 24MHz flash and 40MHz flex clocks, as show in the following simulation:

Regards

Mark

Complete Kinetis solutions for faster/more efficient professional needs, training and support: http://www.utasker.com/kinetis.html

i.MX RT project compatibility: http://www.utasker.com/iMX.html

Including FreeRTOS integration for all Kinetis parts

Kinetis K64:

- http://www.utasker.com/kinetis/FRDM-K64F.html

- http://www.utasker.com/kinetis/TWR-K64F120M.html

- http://www.utasker.com/kinetis/TEENSY_3.5.html

- http://www.utasker.com/kinetis/Hexiwear-K64F.html

uTasker: supporting >1'000 registered Kinetis users get products faster and cheaper to market

Request Free emergency remote desk-top consulting at http://www.utasker.com/services.html

Open Source version at https://github.com/uTasker/uTasker-Kinetis

https://community.nxp.com/thread/512558

https://community.nxp.com/thread/352862

https://community.nxp.com/thread/498809

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Andrew,

In the Reference Manual, in the Clock Distribution Chapter, the internal clocking requirements says that the FlexBus clock frequency must be programmed to 50 Mhz or less and an integer divide of the core clock.

If you are using the SDK, you can know the FlexBus frequency. Use this function from the fsl_clock driver with the kCLOCK_FlexBusClk parameter :

/*!

* @brief Gets the clock frequency for a specific clock name.

*

* This function checks the current clock configurations and then calculates

* the clock frequency for a specific clock name defined in clock_name_t.

* The MCG must be properly configured before using this function.

*

* @param clockName Clock names defined in clock_name_t

* @return Clock frequency value in Hertz

*/

uint32_t CLOCK_GetFreq(clock_name_t clockName);

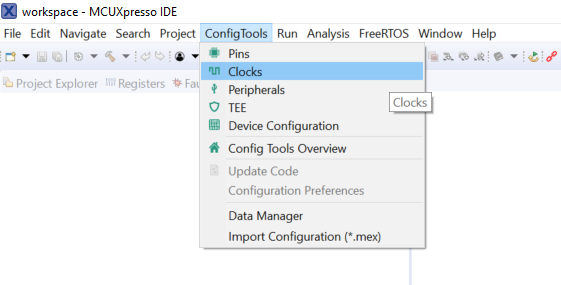

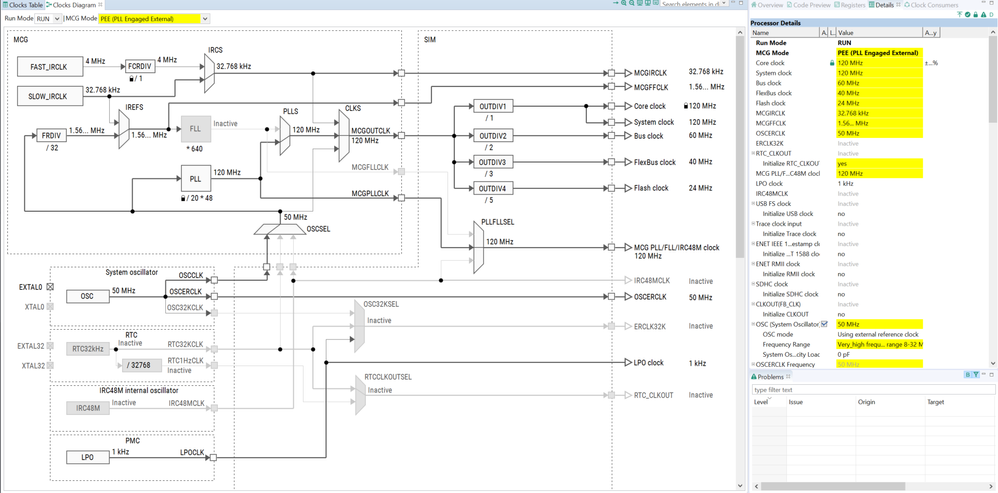

If you need to configurate your clocks, in the MCUXpresso, there is a way to do it in a friendly way, using the ConfigTools.

This tool gives you the clock diagram, where you can see the clocks frequency and configurate them.

You can download the ConfigTools User Guide to know more about this tool.

Best Regards,

Ricardo

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for the information RicardoZamora. I am using KSDK 1.3.0 but it looks like there a similar function called CLOCK_SYS_GetFreq. I was able to determine what our clocks were set to but I'll have to remember this function for future use. We use KDS in our day to day work but I did have a look at MCUXpresso and the Clocks Tool looks great, much easier to understand than the old PE method.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Andrew

See also this for a practical overview of the MCG operation:

http://www.utasker.com/kinetis/MCG.html

It is designed for engineers who want or need to understand exactly what they are doing rather than blindly use code generation.

Regards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Andrew

The bus speeds are set in the register SIM_CLKDIV1, which is usually performed before setting the PLL to its operating speed in order to ensure not overclocking any of the buses (for example, overclocking the flash bus will cause immediate failure).

It is the responsibility of the code to keep to limits - the chip won't limit and an incorrect clock may cause malfunction if actually used.

SIM_CLKDIV1 = 0x01240000; for example (with 120MHz PLL output) gives 120MHz core, 60MHz bus, 24MHz flash and 40MHz flex clocks, as show in the following simulation:

Regards

Mark

Complete Kinetis solutions for faster/more efficient professional needs, training and support: http://www.utasker.com/kinetis.html

i.MX RT project compatibility: http://www.utasker.com/iMX.html

Including FreeRTOS integration for all Kinetis parts

Kinetis K64:

- http://www.utasker.com/kinetis/FRDM-K64F.html

- http://www.utasker.com/kinetis/TWR-K64F120M.html

- http://www.utasker.com/kinetis/TEENSY_3.5.html

- http://www.utasker.com/kinetis/Hexiwear-K64F.html

uTasker: supporting >1'000 registered Kinetis users get products faster and cheaper to market

Request Free emergency remote desk-top consulting at http://www.utasker.com/services.html

Open Source version at https://github.com/uTasker/uTasker-Kinetis

https://community.nxp.com/thread/512558

https://community.nxp.com/thread/352862

https://community.nxp.com/thread/498809

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks mjbcswitzerland. I misplaced my focus on the OUTDIV3 field when really all I had to do was look for the SIM_CLKDIV1 register in our code. Unfortunately I spent a lot of time getting lost in the KSDK clock HAL layer code when in reality the SIM_CLKDIV1 register was being set in the KSDK platform startup files:

From system_MK64F12.c

/* Set system prescalers and clock sources */

SIM->CLKDIV1 = SYSTEM_SIM_CLKDIV1_VALUE; /* Set system prescalers */

From system_MK64F12.h

/* SIM_CLKDIV1: OUTDIV1=0,OUTDIV2=1,OUTDIV3=2,OUTDIV4=4 */

#define SYSTEM_SIM_CLKDIV1_VALUE 0x01240000U /* SIM_CLKDIV1 */

I guess the other thing that got me was that I did not see any mention of the FlexBus clock in Processor Expert.

One of these days I'll get the time to play around with uTasker and avoid some of these headaches :smileyhappy: