- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Re: MK20 SPI doesn't work with disabled FIFO

MK20 SPI doesn't work with disabled FIFO

MK20 SPI doesn't work with disabled FIFO

if I try to use the SPI0 of a MK20DX256 with disabled TX and RK FIFO it doesn't work.

I tried nearly everthing. I use the Config-Tool of Prozessor Expert (only the Init-Module) to set the Init-Parameter.

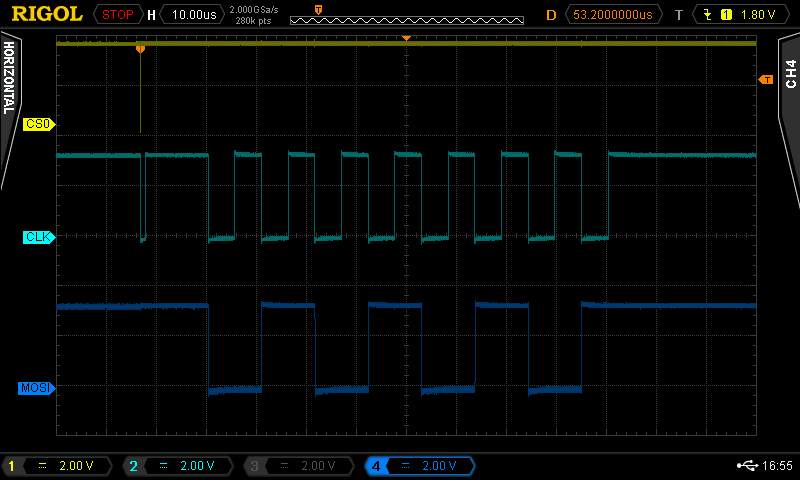

But regardless what I do I got only the frame below.

I init the device (see code below) and write 0xAA the TX_DATA in PUSHR. As you can see it is transmitted but the CS is only a peak

and after this transmission I can do what I want, nothing happens anymore :-( I got no more frames until doing a reset.

Have anyone an idea?

#define STOP_TRANSFER(x) (SPI0_MCR |= SPI_MCR_HALT_MASK);

#define START_TRANSFER (SPI0_MCR |= SPI_MCR_HALT_MASK);

#define SET_CONT_SCKE(x) (SPI0_MCR |= (((uint32)(x & 0x01) << SPI_MCR_CONT_SCKE_SHIFT) & SPI_MCR_CONT_SCKE_MASK))

//Clear the TX FIFO counter

#define CLR_RXF (SPI0_MCR |= SPI_MCR_CONT_SCKE_MASK)

// Clear Transfer Counter

#define CLR_CTCNT (SPI0_PUSHR |= SPI_PUSHR_CTCNT_MASK)

#define SET_CS_CONT(x) (SPI0_PUSHR = SPI0_PUSHR |(((x & 0x01) << SPI_PUSHR_CONT_SHIFT) & SPI_PUSHR_CONT_MASK))

#define SET_PUSHR(command,data) (SPI0_PUSHR = (uint32)command + data)

#define SET_TX_DATA(data) (SPI0_PUSHR = (SPI0_PUSHR & 0xFFFF0000) + data)

#define GET_RX_DATA ((uint8)SPI0_RXFR0)

// Transfer complete? 0 Transfer not complete / 1 Transfer complete

#define GET_TCF ((uint8)((SPI0_SR & SPI_SR_TCF_MASK) >> SPI_SR_TCF_SHIFT))

#define CLR_TCF (SPI0_SR &= ~SPI_SR_TCF_MASK)

// Receive complete? 0 RX FIFO is empty / 1 RX FIFO is not empty

#define GET_RFDF ((uint8)((SPI0_SR & SPI_SR_RFDF_MASK) >> SPI_SR_RFDF_SHIFT))

// this function I call in main()

void Write_Test_Byte(void)

{

// SET_CS_CONT(1); //

// CLR_CTCNT;

// CLR_RXF;

SPI0_PUSHR = (SPI0_PUSHR & 0xFFFF0000) + 0xAA; // send byte

// }

// else return(TRANSMISSION_IS_RUNNING);

for(uint32 j=0; j < 10000; j++)

{

NOP; // wait a while

}

// here breakpoint

// CLR_CTCNT;

// CLR_TCF;

}

/*

** ===================================================================

** Method : SPI0_Init (component Init_SPI)

** Description :

** This method initializes registers of the SPI module

** according to the Peripheral Initialization settings.

** Call this method in user code to initialize the module. By

** default, the method is called by PE automatically; see "Call

** Init method" property of the component for more details.

** Parameters : None

** Returns : Nothing

** ===================================================================

*/

void SPI0_Init(void)

{

/* SIM_SCGC6: SPI0=1 */

SIM_SCGC6 |= SIM_SCGC6_SPI0_MASK;

/* SPI0_MCR: MSTR=0,CONT_SCKE=0,DCONF=0,FRZ=0,MTFE=0,PCSSE=0,ROOE=0,??=0,??=0,PCSIS=0,DOZE=0,MDIS=0,DIS_TXF=0,DIS_RXF=0,CLR_TXF=0,CLR_RXF=0,SMPL_PT=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,HALT=1 */

SPI0_MCR = SPI_MCR_DCONF(0x00) |

SPI_MCR_PCSIS(0x00) |

SPI_MCR_SMPL_PT(0x00) |

SPI_MCR_HALT_MASK;

/* SPI0_MCR: MSTR=1,CONT_SCKE=0,DCONF=0,FRZ=0,MTFE=1,PCSSE=0,ROOE=0,??=0,??=0,PCSIS=1,DOZE=0,MDIS=0,DIS_TXF=1,DIS_RXF=1,CLR_TXF=1,CLR_RXF=1,SMPL_PT=2,??=0,??=0,??=0,??=0,??=0,??=0,??=0,HALT=1 */

SPI0_MCR = SPI_MCR_MSTR_MASK |

SPI_MCR_DCONF(0x00) |

SPI_MCR_MTFE_MASK |

SPI_MCR_PCSIS(0x01) |

SPI_MCR_DIS_TXF_MASK |

SPI_MCR_DIS_RXF_MASK |

SPI_MCR_CLR_TXF_MASK |

SPI_MCR_CLR_RXF_MASK |

SPI_MCR_SMPL_PT(0x02) |

SPI_MCR_HALT_MASK;

/* SPI0_TCR: SPI_TCNT=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SPI0_TCR = SPI_TCR_SPI_TCNT(0x00);

/* SPI0_CTAR0: DBR=0,FMSZ=7,CPOL=1,CPHA=0,LSBFE=0,PCSSCK=3,PASC=3,PDT=3,PBR=1,CSSCK=5,ASC=5,DT=5,BR=7 */

SPI0_CTAR0 = SPI_CTAR_FMSZ(0x07) |

SPI_CTAR_CPOL_MASK |

SPI_CTAR_PCSSCK(0x03) |

SPI_CTAR_PASC(0x03) |

SPI_CTAR_PDT(0x03) |

SPI_CTAR_PBR(0x01) |

SPI_CTAR_CSSCK(0x05) |

SPI_CTAR_ASC(0x05) |

SPI_CTAR_DT(0x05) |

SPI_CTAR_BR(0x07);

/* SPI0_CTAR1: DBR=0,FMSZ=3,CPOL=1,CPHA=0,LSBFE=0,PCSSCK=0,PASC=0,PDT=0,PBR=0,CSSCK=0,ASC=0,DT=0,BR=0 */

SPI0_CTAR1 = SPI_CTAR_FMSZ(0x03) |

SPI_CTAR_CPOL_MASK |

SPI_CTAR_PCSSCK(0x00) |

SPI_CTAR_PASC(0x00) |

SPI_CTAR_PDT(0x00) |

SPI_CTAR_PBR(0x00) |

SPI_CTAR_CSSCK(0x00) |

SPI_CTAR_ASC(0x00) |

SPI_CTAR_DT(0x00) |

SPI_CTAR_BR(0x00);

/* SPI0_SR: TCF=1,TXRXS=0,??=0,EOQF=1,TFUF=1,??=0,TFFF=1,??=0,??=0,??=0,??=0,??=0,RFOF=1,??=0,RFDF=1,??=0,TXCTR=0,TXNXTPTR=0,RXCTR=0,POPNXTPTR=0 */

SPI0_SR = SPI_SR_TCF_MASK |

SPI_SR_EOQF_MASK |

SPI_SR_TFUF_MASK |

SPI_SR_TFFF_MASK |

SPI_SR_RFOF_MASK |

SPI_SR_RFDF_MASK |

SPI_SR_TXCTR(0x00) |

SPI_SR_TXNXTPTR(0x00) |

SPI_SR_RXCTR(0x00) |

SPI_SR_POPNXTPTR(0x00);

/* SPI0_RSER: TCF_RE=0,??=0,??=0,EOQF_RE=0,TFUF_RE=0,??=0,TFFF_RE=0,TFFF_DIRS=0,??=0,??=0,??=0,??=0,RFOF_RE=0,??=0,RFDF_RE=0,RFDF_DIRS=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0,??=0 */

SPI0_RSER = 0x00U;

/* SPI0_MCR: HALT=0 */

SPI0_MCR &= (uint32_t)~(uint32_t)(SPI_MCR_HALT_MASK);

}

yes, I got the same number of frames.... I resolved it in an another way meanwhile.... Thanks!

Yes this works... but leaded to the next problem.

After a reset and the Hardware Init-Routine of SPI0 the TCF is always 0. I have to send a dummy frame to clear it.

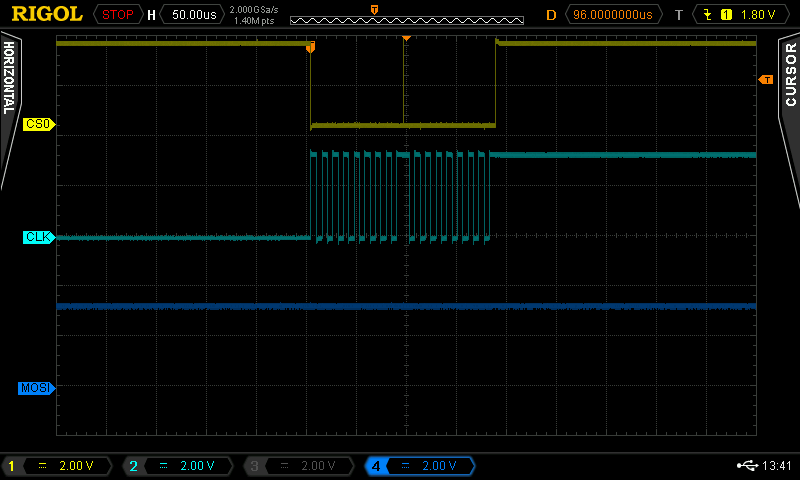

Futhermore I got with this code only to frames. If I have a breakpoint between the commands and execute it step by step

each command send a frame (3 frames). Without breakpoints I got only two frames. Isn't the device already ready when the TCF

is set? Never I had such probems with a SPI device :-(

| #define GET_TCF | (SPI0_SR & SPI_SR_TCF_MASK) |

| SPI0_PUSHR = 0x000100FF; | |

| while(!GET_TCF); | |

| SPI0_PUSHR = 0x000100FF; | |

| while(!GET_TCF); | |

| SPI0_PUSHR = 0x000100FF; | |

| while(!GET_TCF); | |

NOP; |

(no command is sent befor this code)

Hi Marcus,

Do you get the same number of frames if you remove the "while(!GET_TCF);" lines from your code? Also, are you still using your original register settings or have you changed them?

Thank you,

Martyn