- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Re: K20DX256VMD10 SPI slave problem /works on a K20DX256ZVMD10

K20DX256VMD10 SPI slave problem /works on a K20DX256ZVMD10

K20DX256VMD10 SPI slave problem /works on a K20DX256ZVMD10

I am having problems using the K20DX256VMD10 is SPI slave mode, I get an extra zero bit shifted into the RXFIFO resulting in my 32-bit receive frame being shifted one bit to the right. I send (0xE001 0000) but the K20 reads (0x7000 8000). I am using the exact same SPI software I have running on three other projects using a K20DX256ZVMD10 processor, and they all work fine. I have tried this same exact SPI driver software with K40, K60 & K70 tower boards and they all work fine. The only thing I did different is use SPI2 on port-D, where the other projects I use SPI2 on port-B.

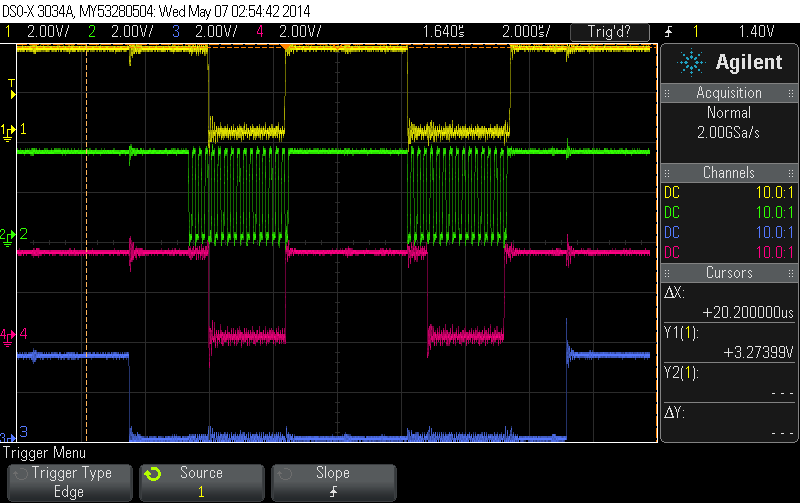

Here is what my 32-bit frame looks like:Yellow is SPI-In, green is clock, red=Out, blue=CS

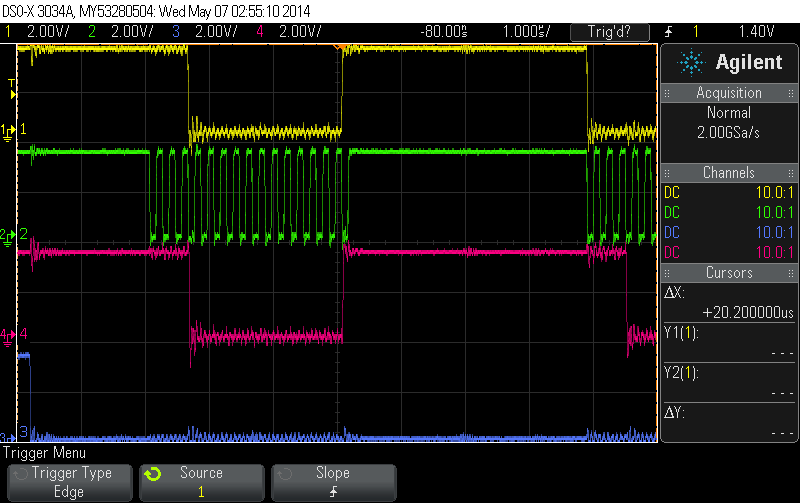

Here is a close-up of the 1st 16-bits:

I am changing on leading edge and capturing on trailing edge. My SPI2_POPR is all zeros at the start, but the K20 sees 0x7000 in the 1st 16-bits, it should see 0xE001, like the scope shows. The 2nd 16-bits reads 0x8000, and the scope clearly shows all zeros.

This is crazy! everything looks good. I plug any of my other three K20DX256ZVMD10 project boards onto this SPI master and they all read (0xE001 0000) just like they should.

Here is my SPI setup code for both projects, the project that works uses SPI2 on port-B, the broke project uses SPI2 on port-D, that is the only difference except the processors are a different flavor (good is MK20DX256ZVMD10, the bad is MK20DX256VMD10)

int_32 spiConfigSpi2Slave()

{

SIM_SCGC3 |= (1UL << SIM_SCGC3_SPI2_SHIFT); // Enable SPI2

SIM_SCGC5 |= (1UL << SIM_SCGC5_PORTD_SHIFT); // Enable Clock to Port D for new Qlx cards.

SIM_SCGC5 |= (1UL << SIM_SCGC5_PORTB_SHIFT); // Enable Clock to Port D for new Qlx cards.

SPI2_SR |= SPI_SR_RFDF_MASK | SPI_SR_RFOF_MASK ; // Clear the SPI2 slave interrupt

SPI2_RSER = (1UL << SPI_RSER_RFDF_RE_SHIFT); // SPI2 interrupt when SPI2 RX FIFO is not empty

SPI2_CTAR0_SLAVE = TJ32BIT_SPI_SLAVE; // TJdriver-32 bits slave SPI, clk idle high, trailing edge capture.

SPI2_MCR = ((1UL << SPI_MCR_CONT_SCKE_SHIFT)

| (1UL << SPI_MCR_MTFE_SHIFT)

| (1UL << SPI_MCR_CLR_RXF_SHIFT)

| (1UL << SPI_MCR_PCSIS_SHIFT) ); // Continuous, modified timing, run SPI

#if REAL_SCALE_CARD // for the real new scale card

// Setup processor pins for SPI.

PORTD_PCR11 = (1UL << 9); //SPI alt2, CS0

PORTD_PCR12 = (1UL << 9); //SPI alt2, Clock

PORTD_PCR13 = ((1UL << 9) | (1UL << 6)); //SPI alt2, Out set to hi-drive power

PORTD_PCR14 = (1UL << 9); //SPI alt2, In

#else

PORTB_PCR20 = (1UL << 9); //SPI alt2, CS0

PORTB_PCR21 = (1UL << 9); //SPI alt2, Clock

PORTB_PCR22 = ((1UL << 9) | (1UL << 6)); //SPI alt2, Out set to hi-drive power

PORTB_PCR23 = (1UL << 9); //SPI alt2, In

#endif

SPI2_MCR |= (1UL << SPI_MCR_CLR_RXF_SHIFT); // clear RXFIFO counter

return(MQX_OK);

}

If anyone has an idea of what my problem is I would appreciate some help. Thanks in advance.

Cheers,

Tom

Hi Tom,

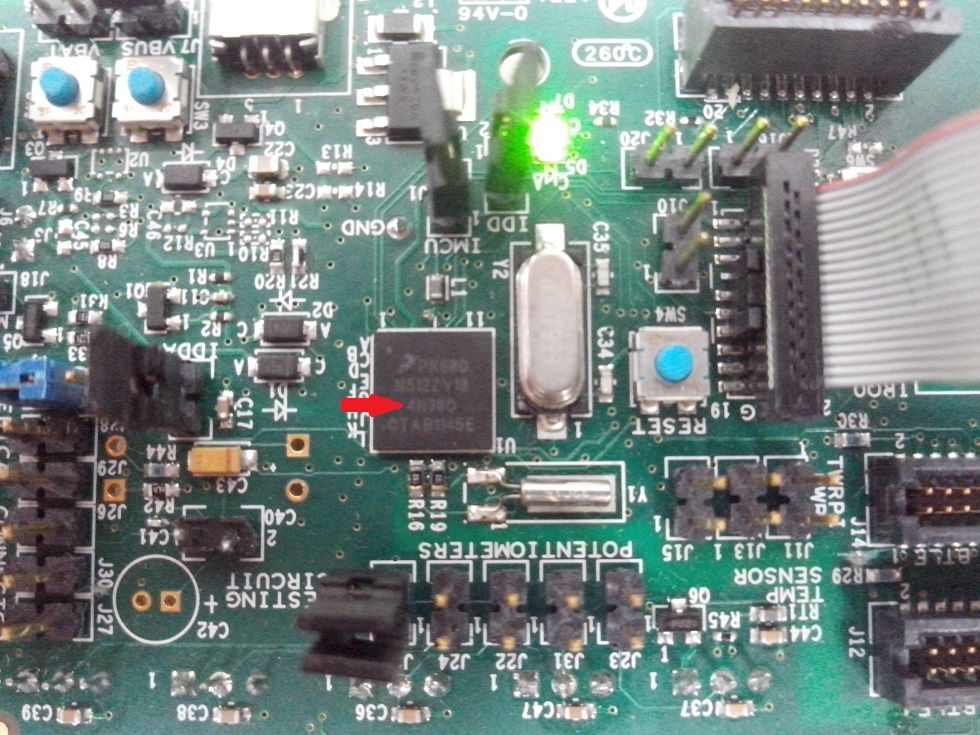

Can you share with us the silicon mask of your functioning and non-functioning devices. The silicon mask is printed below the part number on the microcontroller (See image)

Saludos

Santiago Lopez

Hey Santiago Lopez,

4N22D is the mask, But the problem seems to be in my court. I just now realized I did a board a while back that uses this same part and the same SPI port and pins, and that board works. And my new code runs the same on that board (bad) but it runs good on another board with the other K20. Weird, but at least I know I can make it work.

Gracias por ayuda.

Cheers,

Tom