- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Flexbus write cycle

Flexbus write cycle

Hi,

I have 16-bit SRAM connected to K22 via Flexbus. Port size of Flexbus is set to 16-bit. No delays are introduced in write/read cycles (I mean WS/ASET/RDAH/WRAH re all set to 0). This is my configuration:

FB->CS[0].CSCR = FB_CSCR_PS(2)

| FB_CSCR_BLS_MASK

| FB_CSCR_ASET(0x0)

| FB_CSCR_RDAH(0x0)

| FB_CSCR_WRAH(0x0)

| FB_CSCR_AA_MASK

| FB_CSCR_WS(0x0)

;

I write 32 bit integer into my memory:

volatile int *sram;

sram = SRAM_START_ADDRESS;

sram[0] = 0;

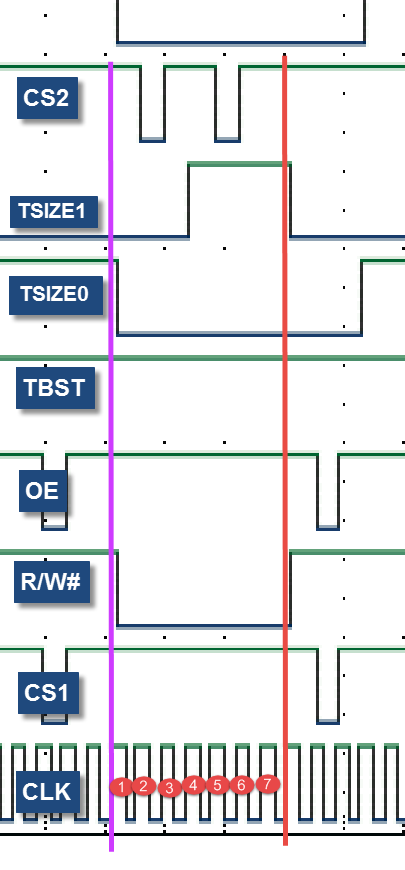

I can see that writing first part of my 32 bit integer takes only 3 flexbus clock cycles. (in the picture you can see three 32 bit integer writes to the 16 bit memory)

In all documents I read flexbus read/write cycles take 4 clock cycles min. Can you please help me in understanding this 3 clock cycle write?

已解决! 转到解答。

Hi Martin,

I got the feedback from Kinetis product team with below feedback:

In this case, a 32-bit access is launched on a 16-bit port, that means there would definitely be two continuous accesses here.

In fact, S3 is used to terminate the transfer, so in this case, it is reasonable that the 1st access skipped S3 and goes to S0 directly, so it only take 3 clocks here.

But in the second access(it is writing here), S3 is a must to terminate the transfer.

We have a Flexbus timing about read from 8-bit port size device and write to 16-bit port device with 32-bit access (WS/ASET/RDAH/WRAH re all set to 0).

Please check attached picture for detailed info.

I zoom in the 32-bit write to 16-bit port device and get there take 7 Flexbus clock cycles, the first 16-bit write take 3 Flexbus clock cycles:

Wish it helps.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi,

From the scope picture, the write operation with 3 Flexbus cycles.

Could you provide the more detailed Flexbus setting?

What's the SRAM_START_ADDRESS value?

What's the Flexbus clock frequency?

If possible, could you provide Flexbus initialization code?

Thank you.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Mike,

my initialization code (I do not post pin function initialization):

#define RAM_START_ADDRESS 0x18000000

void FlexBusInit() {

SIM->SCGC7 |= SIM_SCGC7_FLEXBUS_MASK;

FB->CSPMCR = FB_CSPMCR_GROUP1(2);

FB->CS[0].CSAR = RAM_START_ADDRESS;

FB->CS[0].CSCR = FB_CSCR_PS(2)

| FB_CSCR_BLS_MASK

| FB_CSCR_ASET(0x0)

| FB_CSCR_RDAH(0x0)

| FB_CSCR_WRAH(0x0)

| FB_CSCR_AA_MASK

| FB_CSCR_WS(0x0);

FB->CS[0].CSMR = FB_CSMR_BAM(0x7) | FB_CSMR_V_MASK;

}

Flexbus clock is 30 MHz, can bee seen on the scope printscreen.

Hi

From the Flexbus initialization code, there without any issue.

Could you post the Flebux registers value after initialization?

Please make sure there doesn't enable the burst write.

When you do a 16-bit operation, the Flexbus write operation will be 4 cycles?

Thanks.

best regards,

Mike

Hi,

when I perform 16 bit write on 120 MHz CPU frequency:

volatile short *flex = SRAM_START_ADDRESS;

while(1) {

flex[0] = 5;

}

I can see 4 flexbus clock cycles between every FB_TS assertion on my scope so I guess I can confirm that 16 bit write cycle takes 4 flexbus cycles.

Flexbus registers after initialization:

CSAR0 = 0x18000000

CSMR0 = 0x00070001

CSCR0 = 0x00000380

CSPMCR = 0x20000000

Hi,

Thank you for the test.

I need to check with Kinetis product team about why the 32-bit write to 16-bit port, the first write operation with only 3 Flexbus clock cycles.

I will let you know when there with any feedback.

Thank you for the patience.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Martin,

I got the feedback from Kinetis product team with below feedback:

In this case, a 32-bit access is launched on a 16-bit port, that means there would definitely be two continuous accesses here.

In fact, S3 is used to terminate the transfer, so in this case, it is reasonable that the 1st access skipped S3 and goes to S0 directly, so it only take 3 clocks here.

But in the second access(it is writing here), S3 is a must to terminate the transfer.

We have a Flexbus timing about read from 8-bit port size device and write to 16-bit port device with 32-bit access (WS/ASET/RDAH/WRAH re all set to 0).

Please check attached picture for detailed info.

I zoom in the 32-bit write to 16-bit port device and get there take 7 Flexbus clock cycles, the first 16-bit write take 3 Flexbus clock cycles:

Wish it helps.

Have a great day,

Mike

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------