- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- FRDM K64F Dual SPI interface with AD7606B Not Working

FRDM K64F Dual SPI interface with AD7606B Not Working

Hi,

i am trying to interface AD7606B ADC IC with FRDM-k64F by Dual SPI interface similar to the Solution 4 in the link Below.

https://www.analog.com/en/analog-dialogue/raqs/raq-issue-172.html

in my case

SPI0 is Master ( working properly )

SPI1 is Slave. ( Not working )

i want to read AD7606B as fast as possible.

with single SPI it is working But in Dual SPI interface slave is not working.

Attached is the code file

SPI configuration

/* Master config */

masterConfig.whichCtar = kDSPI_Ctar0;

masterConfig.ctarConfig.baudRate = TRANSFER_BAUDRATE;

masterConfig.ctarConfig.bitsPerFrame = 16U;

masterConfig.ctarConfig.cpol = kDSPI_ClockPolarityActiveHigh;

masterConfig.ctarConfig.cpha = kDSPI_ClockPhaseFirstEdge;

masterConfig.ctarConfig.direction = kDSPI_MsbFirst; //kDSPI_LsbFirst // kDSPI_MsbFirst

masterConfig.ctarConfig.pcsToSckDelayInNanoSec = 1000000000U / TRANSFER_BAUDRATE;

masterConfig.ctarConfig.lastSckToPcsDelayInNanoSec = 1000000000U / TRANSFER_BAUDRATE;

masterConfig.ctarConfig.betweenTransferDelayInNanoSec = 1000000000U / TRANSFER_BAUDRATE;

masterConfig.whichPcs = EXAMPLE_DSPI_MASTER_PCS_FOR_INIT;

masterConfig.pcsActiveHighOrLow = kDSPI_PcsActiveLow;

masterConfig.enableContinuousSCK = false;

masterConfig.enableRxFifoOverWrite = false;

masterConfig.enableModifiedTimingFormat = false;

masterConfig.samplePoint = kDSPI_SckToSin0Clock;

srcClock_Hz = DSPI_MASTER_CLK_FREQ;

DSPI_MasterInit(EXAMPLE_DSPI_MASTER_BASEADDR, &masterConfig, srcClock_Hz);

/* Slave config */

slaveConfig.whichCtar = kDSPI_Ctar0;

slaveConfig.ctarConfig.bitsPerFrame = masterConfig.ctarConfig.bitsPerFrame;

slaveConfig.ctarConfig.cpol = masterConfig.ctarConfig.cpol;

slaveConfig.ctarConfig.cpha = masterConfig.ctarConfig.cpha;

slaveConfig.enableContinuousSCK = masterConfig.enableContinuousSCK;

slaveConfig.enableRxFifoOverWrite = masterConfig.enableRxFifoOverWrite;

slaveConfig.enableModifiedTimingFormat = masterConfig.enableModifiedTimingFormat;

slaveConfig.samplePoint = masterConfig.samplePoint;

DSPI_SlaveInit(EXAMPLE_DSPI_SLAVE_BASEADDR, &slaveConfig);

// DSPI_SlaveTransferCreateHandle(EXAMPLE_DSPI_SLAVE_BASEADDR, &g_s_handle, DSPI_SlaveUserCallback, NULL);

///* Set slave transfer to receive data */

// isTransferCompleted = false;

slaveXfer.txData = NULL;

slaveXfer.rxData = slaveRxData;

slaveXfer.dataSize = TRANSFER_SIZE;

slaveXfer.configFlags = kDSPI_SlaveCtar0;

GPIO_PortSet(GPIOC, 1U << BOARD_RESET_AD_PIN); //PTC3 RESET

//SysTick_DelayTicks(1U); // Delay 1000 ms

for (i = 0; i < 12000; i++)

{__NOP();}

GPIO_PortClear(GPIOC, 1U << BOARD_RESET_AD_PIN); //PTC3 RESET

GPIO_PortSet(GPIOE, 1U << 25U);

/* Start master transfer, receive data from slave */

masterXfer.txData = NULL;

masterXfer.rxData = masterRxData;

masterXfer.dataSize = TRANSFER_SIZE; //kDSPI_MasterPcsContinuous

masterXfer.configFlags = kDSPI_MasterCtar0 | EXAMPLE_DSPI_MASTER_PCS_FOR_TRANSFER | kDSPI_MasterActiveAfterTransfer; //kDSPI_MasterActiveAfterTransfer

slaveXfer.txData = NULL;

slaveXfer.rxData = slaveRxData;

slaveXfer.dataSize = TRANSFER_SIZE;

slaveXfer.configFlags = kDSPI_SlaveCtar0;

assert(NULL != &masterXfer);

uint16_t wordToSend = 0;

uint16_t wordReceived = 0;

uint8_t dummyData = DSPI_GetDummyDataInstance(EXAMPLE_DSPI_MASTER_BASEADDR);

uint8_t bitsPerFrame;

uint32_t command;

uint32_t lastCommand;

uint16_t *txData;

uint16_t *rxData;

uint32_t fifoSize;

uint32_t tmpMCR = 0;

dspi_command_data_config_t commandStruct;

/* If the transfer count is zero, then return immediately.*/

if (&masterXfer.dataSize == 0U)

{

return kStatus_InvalidArgument;

}

DSPI_StopTransfer(EXAMPLE_DSPI_MASTER_BASEADDR);

DSPI_DisableInterrupts(EXAMPLE_DSPI_MASTER_BASEADDR, (uint32_t)kDSPI_AllInterruptEnable);

DSPI_FlushFifo(EXAMPLE_DSPI_MASTER_BASEADDR, true, true);

DSPI_StopTransfer(EXAMPLE_DSPI_SLAVE_BASEADDR);

DSPI_DisableInterrupts(EXAMPLE_DSPI_SLAVE_BASEADDR, (uint32_t)kDSPI_AllInterruptEnable);

DSPI_FlushFifo(EXAMPLE_DSPI_SLAVE_BASEADDR, true, true);

/*Calculate the command and lastCommand*/

commandStruct.whichPcs =

(dspi_which_pcs_t)(1U << ((masterXfer.configFlags & DSPI_MASTER_PCS_MASK) >> DSPI_MASTER_PCS_SHIFT));

commandStruct.isEndOfQueue = false;

commandStruct.clearTransferCount = false;

commandStruct.whichCtar =

(dspi_ctar_selection_t)((masterXfer.configFlags & DSPI_MASTER_CTAR_MASK) >> DSPI_MASTER_CTAR_SHIFT);

commandStruct.isPcsContinuous =

(0U != (masterXfer.configFlags & (uint32_t)kDSPI_MasterPcsContinuous)) ? true : false;

command = DSPI_MasterGetFormattedCommand(&(commandStruct));

commandStruct.isEndOfQueue = true;

commandStruct.isPcsContinuous =

(0U != (masterXfer.configFlags & (uint32_t)kDSPI_MasterActiveAfterTransfer)) ? true : false;

lastCommand = DSPI_MasterGetFormattedCommand(&(commandStruct));

DSPI_SetFifoEnable(EXAMPLE_DSPI_MASTER_BASEADDR,false,false);

DSPI_SetFifoEnable(EXAMPLE_DSPI_SLAVE_BASEADDR,false,false);

/*Calculate the bitsPerFrame*/

bitsPerFrame = (uint8_t)(((EXAMPLE_DSPI_MASTER_BASEADDR->CTAR[commandStruct.whichCtar] & SPI_CTAR_FMSZ_MASK) >> SPI_CTAR_FMSZ_SHIFT) + 1U);

tmpMCR = EXAMPLE_DSPI_MASTER_BASEADDR->MCR;

if ((0U != (tmpMCR & SPI_MCR_DIS_RXF_MASK)) || (0U != (tmpMCR & SPI_MCR_DIS_TXF_MASK)))

{

fifoSize = 1U;

}

else

{

fifoSize = FSL_FEATURE_DSPI_FIFO_SIZEn(EXAMPLE_DSPI_MASTER_BASEADDR);

}

fifoSize=1U;

data Reading Part

while (1)

{

rxData1=0;

GPIO_PortClear(GPIOC, 1U << 4U); //PTC4 Convst

GPIO_PortSet(GPIOC, 1U << 4U); //PTC4 Convst

while(GPIO_PinRead(GPIOC, 12U) == true){;

//wait for conversions to be completed

}

DSPI_ClearStatusFlags(EXAMPLE_DSPI_MASTER_BASEADDR, (uint32_t)kDSPI_AllStatusFlag);

DSPI_ClearStatusFlags(EXAMPLE_DSPI_SLAVE_BASEADDR, (uint32_t)kDSPI_AllStatusFlag);

//txData = masterXfer.txData;

//rxData = masterXfer.rxData;

remainingSendByteCount = masterXfer.dataSize;

remainingReceiveByteCount = masterXfer.dataSize;

EXAMPLE_DSPI_MASTER_BASEADDR->MCR &= ~SPI_MCR_HALT_MASK;

EXAMPLE_DSPI_SLAVE_BASEADDR->MCR &= ~SPI_MCR_HALT_MASK;

while (remainingSendByteCount > 0U)

{

if (remainingSendByteCount <= 2U)

{

wordToSend = dummyData;

EXAMPLE_DSPI_MASTER_BASEADDR->PUSHR = lastCommand | wordToSend; //Master send Dummy DATA

// EXAMPLE_DSPI_SLAVE_BASEADDR->PUSHR = lastCommand | wordToSend; //Slave send Dummy DATA

EXAMPLE_DSPI_MASTER_BASEADDR->SR = (uint32_t)kDSPI_TxFifoFillRequestFlag; /*!< The status flags are cleared by writing 1 (w1c).*/

EXAMPLE_DSPI_SLAVE_BASEADDR->SR = (uint32_t)kDSPI_TxFifoFillRequestFlag; /*!< The status flags are cleared by writing 1 (w1c).*/

remainingSendByteCount -= 2U;

while (remainingReceiveByteCount > 0U)

{

if ((uint32_t)kDSPI_RxFifoDrainRequestFlag ==

(EXAMPLE_DSPI_MASTER_BASEADDR->SR & (uint32_t)kDSPI_RxFifoDrainRequestFlag))

{

masterRxData[rxData1] = (uint16_t)EXAMPLE_DSPI_MASTER_BASEADDR->POPR; //read Master

EXAMPLE_DSPI_MASTER_BASEADDR->SR = (uint32_t)kDSPI_RxFifoDrainRequestFlag;

slaveRxData[rxData1] = (uint16_t)EXAMPLE_DSPI_SLAVE_BASEADDR->POPR; //read slave

EXAMPLE_DSPI_SLAVE_BASEADDR->SR = (uint32_t)kDSPI_RxFifoDrainRequestFlag;

++rxData1;

remainingReceiveByteCount -= 2U;

}

}

}

else

{

wordToSend = dummyData;

EXAMPLE_DSPI_MASTER_BASEADDR->PUSHR = command | wordToSend;

EXAMPLE_DSPI_SLAVE_BASEADDR->PUSHR = command | wordToSend;

remainingSendByteCount -= 2U;

EXAMPLE_DSPI_MASTER_BASEADDR->SR = (uint32_t)kDSPI_TxFifoFillRequestFlag;

EXAMPLE_DSPI_SLAVE_BASEADDR->SR = (uint32_t)kDSPI_TxFifoFillRequestFlag;

while (((remainingReceiveByteCount - remainingSendByteCount) / 2U) >= fifoSize)

{

if ((uint32_t)kDSPI_RxFifoDrainRequestFlag ==

(EXAMPLE_DSPI_MASTER_BASEADDR->SR & (uint32_t)kDSPI_RxFifoDrainRequestFlag))

{

masterRxData[rxData1] = (uint16_t)EXAMPLE_DSPI_MASTER_BASEADDR->POPR; //read Master

EXAMPLE_DSPI_MASTER_BASEADDR->SR = (uint32_t)kDSPI_RxFifoDrainRequestFlag;

slaveRxData[rxData1] = (uint16_t)EXAMPLE_DSPI_SLAVE_BASEADDR->POPR; //read Slave

EXAMPLE_DSPI_SLAVE_BASEADDR->SR = (uint32_t)kDSPI_RxFifoDrainRequestFlag;

++rxData1;

remainingReceiveByteCount -= 2U;

}

}

}

}

int ii=0;

for (int k = 0; k < 8; k++) {

// highByte = masterRxData[ii+1];

// lowByte = masterRxData[ii];

// ii=ii+2;

datavoltages[k] = ((int16_t)(masterRxData[k]))*qq;

datavoltages[k+4] = ((int16_t)(slaveRxData[k]))*qq;

}

}

}

已解决! 转到解答。

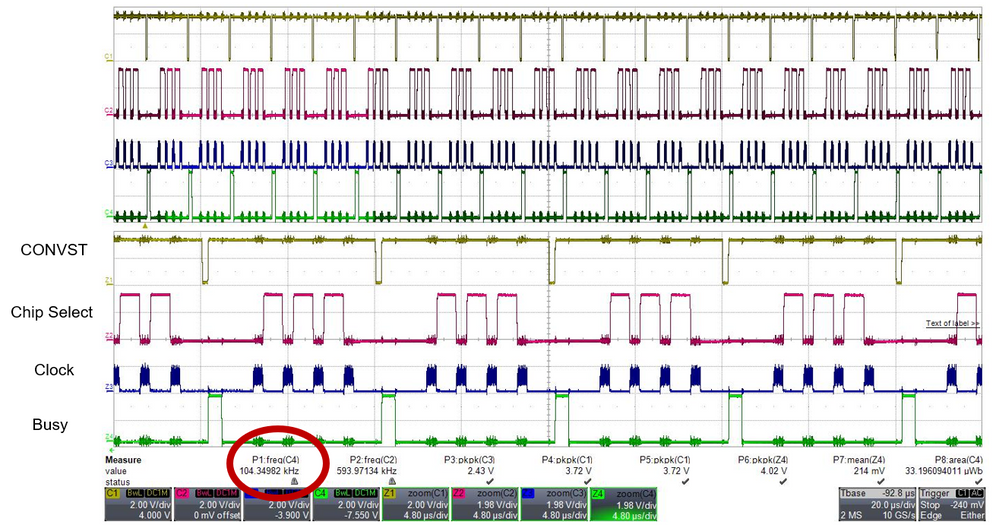

Thanks for your reply. Actually i was able to solve the problem. the code was working fine. i was able to get 104ksps.

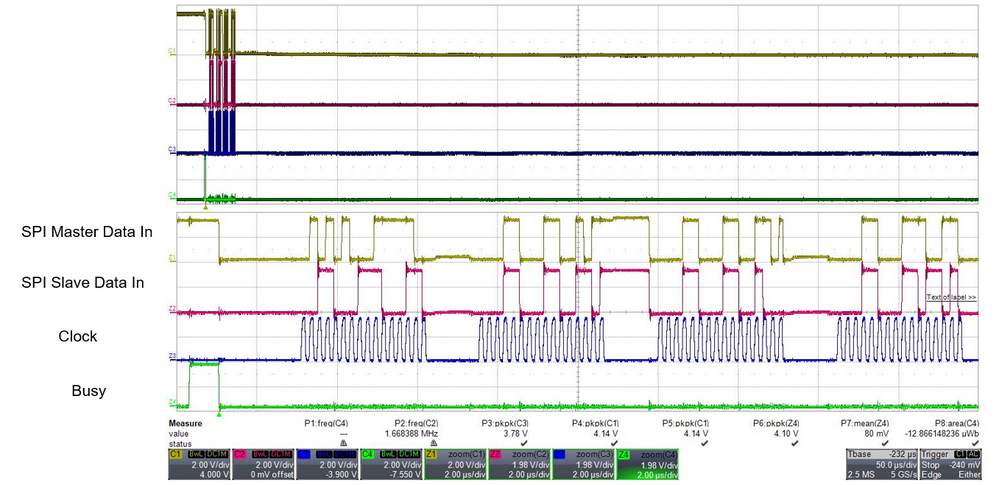

i didn't connected the MOSI (FRDM) > SDI (ad7606b). after connecting them the slave was able to read the data as well. i am not using the MOSI as i am using hardware mode so i didn't connected it before. below are some captures.

below is the spi sampling speed capture

i have two more questions.

1) Is there a way to increase the sampling speed?

2) the 16bit data i received is right shifted for all 8 channels.

ie instead of 0010 1010 0011 1011

i am getting 0001 0101 0001 1101

Regards.

Hello @GRK ,

1) The sampling of the slave is according to the bus clock and should be able to sample the signal without problems.

2) Can you try connecting the master interface to the slave interface to check if the problem is the sampling rate or something with the ADC?

Best Regards,

Alexis Andalon

Thanks for your reply. Actually i was able to solve the problem. the code was working fine. i was able to get 104ksps.

i didn't connected the MOSI (FRDM) > SDI (ad7606b). after connecting them the slave was able to read the data as well. i am not using the MOSI as i am using hardware mode so i didn't connected it before. below are some captures.

below is the spi sampling speed capture

i have two more questions.

1) Is there a way to increase the sampling speed?

2) the 16bit data i received is right shifted for all 8 channels.

ie instead of 0010 1010 0011 1011

i am getting 0001 0101 0001 1101

Regards.