- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior for QorIQ

- :

- Re: some items of DDR configuration?

some items of DDR configuration?

some items of DDR configuration?

1. my board SMT Memory Cell directly, and no spd eeprom , so i should select the discrete dram?

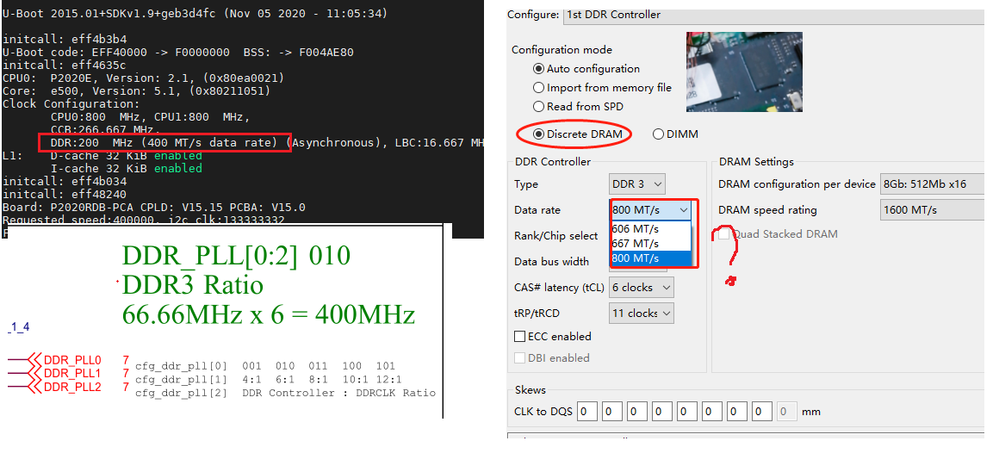

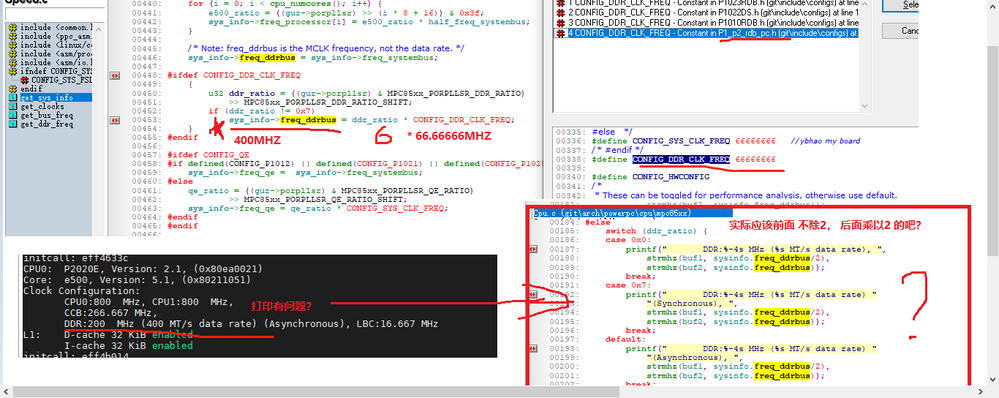

2. what's the difference between “DDR :200MHZ " and " DDR date rate 400MT/s ", the DDRCLK is set to 400MHZ by starpping pin, the uboot message is right?

i think it should be print “DDR : 400MHZ” and " DDR date rate 800MT/s ",so this is uboot bug?

3. i don't see the " DDR date rate 400MT/s " in QCVS ddr configuration tabs, why?

4. clk to DQS skews, ----- is the Length difference ?

abs(DQS0 of length - (CLK_cpu to CLK_ic1 of length))

abs(DQS1 of length - (CLK_cpu to CLK_ic1 of length))

abs(DQS2 of length - (CLK_cpu to CLK_ic2 of length))

abs(DQS3 of length - (CLK_cpu to CLK_ic2 of length))

abs(DQS4 of length - (CLK_cpu to CLK_ic3 of length))

abs(DQS5 of length - (CLK_cpu to CLK_ic3 of length))

abs(DQS6 of length - (CLK_cpu to CLK_ic4 of length))

abs(DQS7 of length - (CLK_cpu to CLK_ic4 of length))

thank you very much !

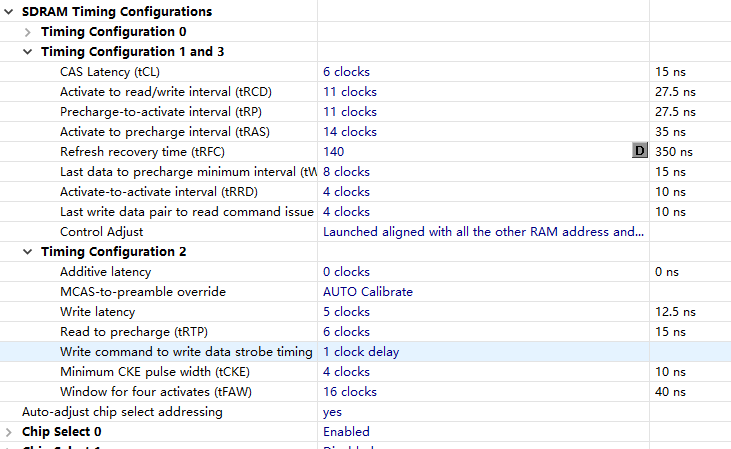

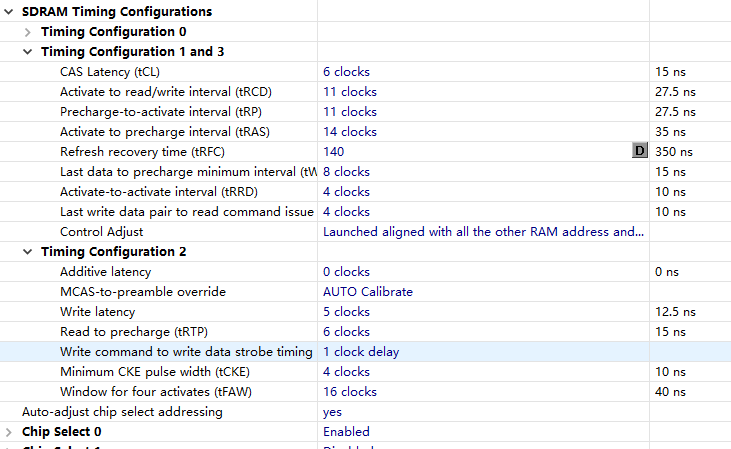

1. does i can use the timing of above as default init value before learning ? if not , which critical param should i set , have some document?

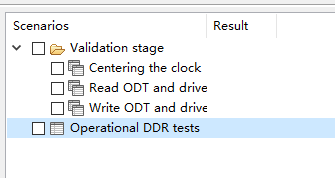

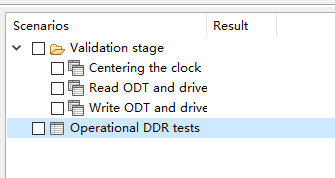

2. which script sould i run?

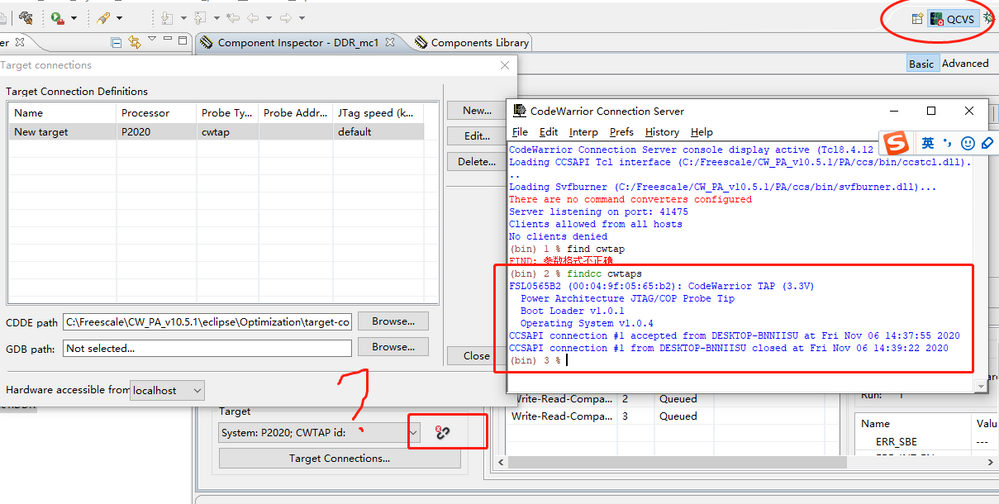

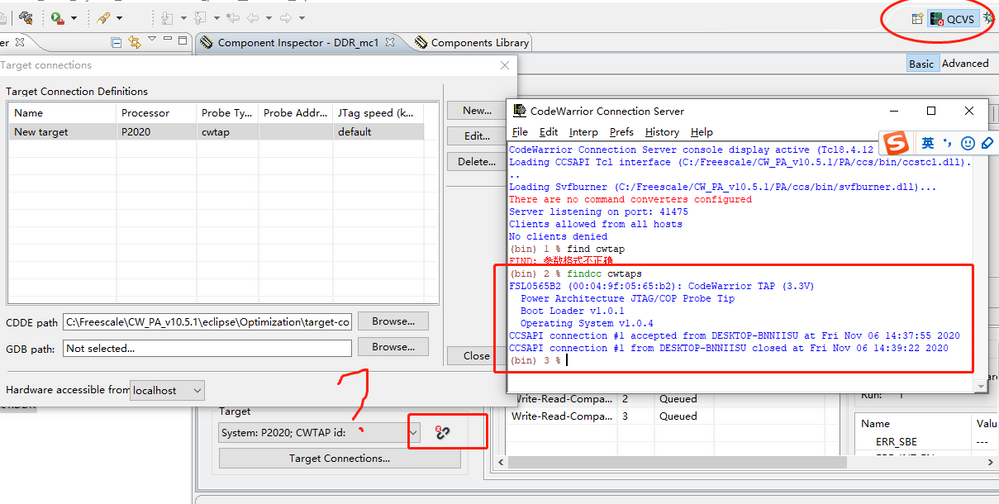

now i can find cwtaps at ccs, and can connect chip at debug mode. but at QCVS mode ,i can't connect , thank you

thank you very much!

1. does the timing of above can be use default value before learning cycle ? if not, which Critical parameter should i set,have some document to reference?

2. all the script of the above should be run?

i can find my cwtaps at ccs, but i can‘t connect chip at QCVS , help me, and i can connect chip at debug mode now。

thanks

1. You could select discrete dram.

2. u-boot is correct, DDR clock frequency is 66.66/2*6=200MHz, data rate is 400MT/s.

3. Please create a QCVS DDR project, then double click "DDR_mc1:DDR" component to show Properties panel, you could configure "DDR Bus Clock" as 200MHz in the Properties panel.

4. The Length is different.

Please refer to the section "System clock and DDR controller clock" in P2020 Reference Manual.

If further discussion is needed, please create new a thread in https://community.nxp.com/t5/QorIQ/bd-p/qoriq-grl, the hardware team will help to explain more.