- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- CodeWarrior

- :

- CodeWarrior Development Tools

- :

- How to enable to generated ISR OnHardFault Code using PE

How to enable to generated ISR OnHardFault Code using PE

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have K60 tower board. I have MQX 4.2 and Code Warrior 10.6.4.

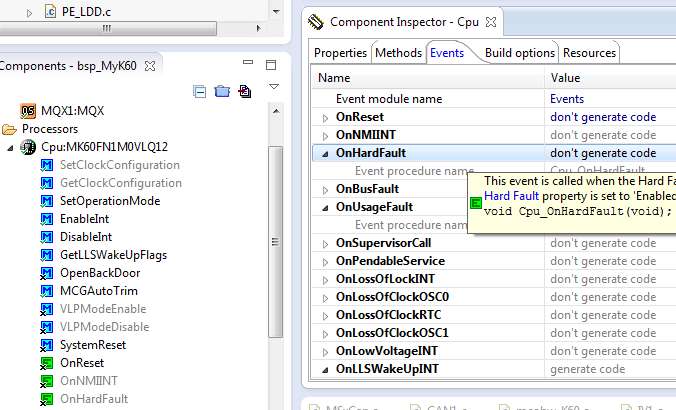

I want to generate code for Cpu_OnHardFault ISR using PE, but it is disabled. I am not sure there is any way to enable it for generate code:

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

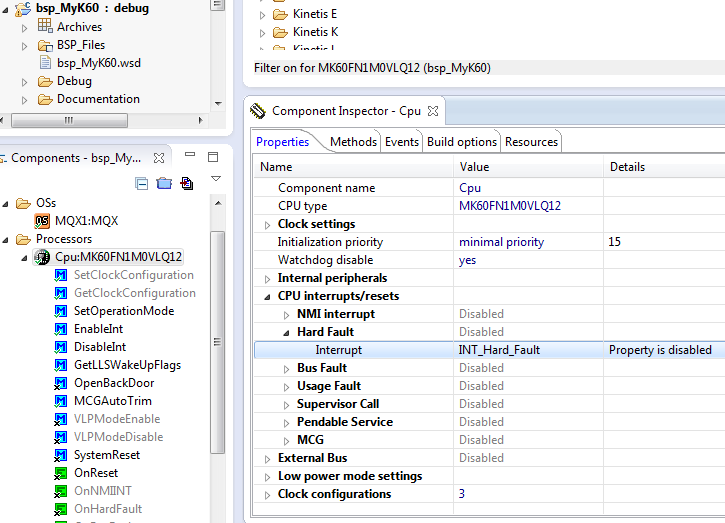

I think the reason that you cannot enable it the usual way is because you have MQX in your project: MQX takes ownership of all interrupts.

I hope this helps,

Erich

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David

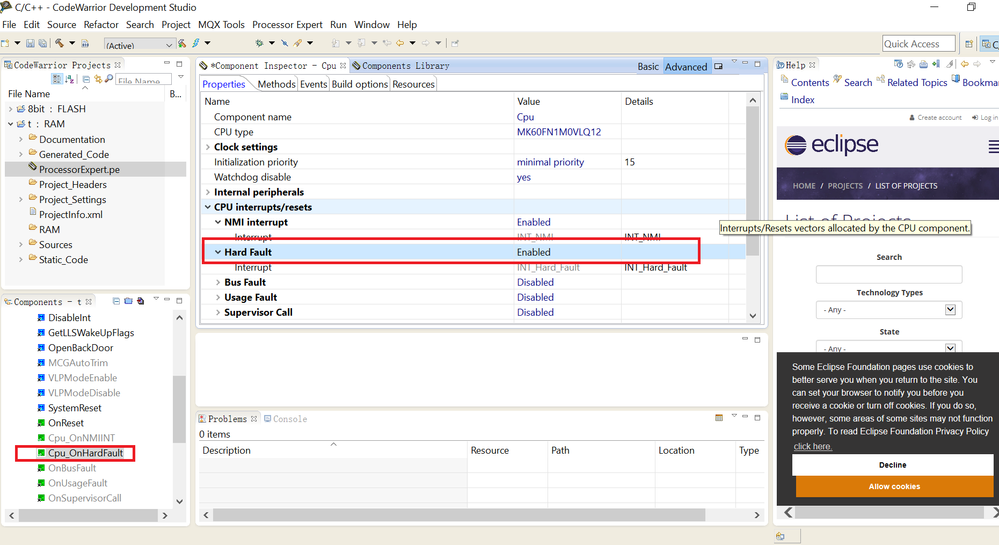

This feature is automatically enabled when the hard fault property is set to "Enabled". see below screenshot.

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jennie,

Thank you for your reply. In my PE, all the interrupts are disabled, and I cannot find a way to enable them. See the screen pasted below:

When I left-click the OnHardFault, there is a popup menu to toggle Enable/Disable, but it is GRAYED.

it must have another level of enabling it. I don't know the small green icon with a little cross on it. Enabled ones are blue with a check.

Thank you,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

I agree that this might be confusing. But the it means that the *property' is disabled and cannot be changed, as the HardFault cannot be disabled. So it is turned on anyway by the hardware as it is a non-maskable interrupt.

I hope this helps,

Erich

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Erich, Jennie,

Thanks for explanation. But I still don't know how to enable it as Jennie's saved screen with ENABLE to generated code for the HardFault ISR. From my screen pasted, all those functions are disabled, AND I have a no way to ENABLE them. That results in preventing me from generating code for them. I understand they are non-maskable interrupts, currently are all tied into _int_kernel_isr. Do you mean non-maskable interrupts can not generated code from PE? But then why Jennie's screen shows enable and be able to generate code?

Thank you,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

I think the reason that you cannot enable it the usual way is because you have MQX in your project: MQX takes ownership of all interrupts.

I hope this helps,

Erich

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Erich,

Thank you for the answer. That explains. As I have said I have manually installed the ISR, it is not a problem for me.

Best Regards,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

By the way, I have created a function CW_InstallIsrHardFault and manually installed ISR for the OnHardFault as follows:

uint32_t CW_InstallIsrHardFault(INT_ISR_FPTR isr) {

INT_ISR_FPTR fpISR;

fpISR = _int_install_isr(3, isr, (void *)NULL);

if ( fpISR == (INT_ISR_FPTR) NULL ) {

return 1;

}

return 0;

}

Thanks,

David