- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: MPC5775K FlexPWM ETimer

MPC5775K FlexPWM ETimer

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5775K FlexPWM ETimer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The FlexPWM module is independent of used core.

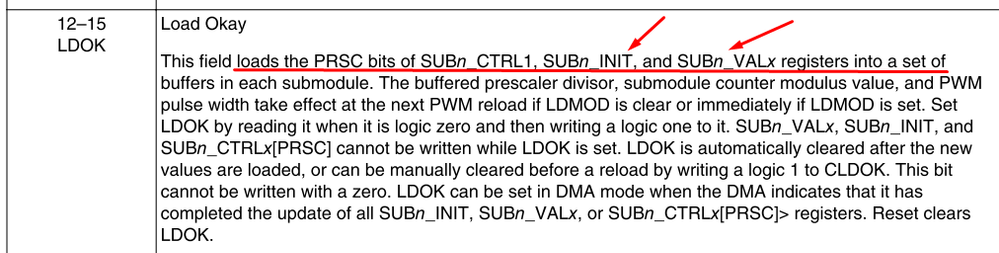

Your code is missing LDOK bit set for particular module. Without LDOK set the values in FlexPWM registers are still as default. as it is well described in RM.

Please follow the example codes.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks. My project seems work now. The PWM module is able to work only when I reset the power.

There may be something more I should do. But I'm not clear at the moment.

I correct the code like this:

// D[9] pin as FlexPWM X[0] output

SIUL2.MSCR[57].R = 0x02800001;

//GPIO[57]

//PWM X0

FlexPWM_0.OUTEN.R = 0x001; // enable A,B and X outputs on submodule 0

FlexPWM_0.SUB[0].CTRL1.R = 0x0400; // full cycle reload, every opportunity,IPBus/1

FlexPWM_0.SUB[0].CTRL2.R = 0x2000; // independent pair operation

FlexPWM_0.SUB[0].DTCNT0.R = 0x0000; // deadtime values, not aplicable on INDEP mode

FlexPWM_0.SUB[0].DTCNT1.R = 0x0000;

FlexPWM_0.SUB[0].INIT.R = 0x0; // PWM init value

FlexPWM_0.SUB[0].VAL1.R = PWM_PERIOD; // PWM modulo, PWMX falling edge

FlexPWM_0.SUB[0].VAL0.R = PWM_DUTY; // PWMX rising edge, half cycle reload point

FlexPWM_0.SUB[0].VAL2.R = 0; // PWM A0 rising edge

FlexPWM_0.SUB[0].VAL3.R = 0; // PWM A0 falling edge

FlexPWM_0.SUB[0].VAL4.R = 0; // PWM B0 rising edge

FlexPWM_0.SUB[0].VAL5.R = 0; // PWM B0 falling edge

FlexPWM_0.SUB[0].DISMAP.R = 0x0000; // disable fault pin condition

FlexPWM_0.MCTRL.B.LDOK = 0x1;

FlexPWM_0.MCTRL.B.RUN = 0x1; // Submodule 0 PWM generator enabled

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Always check community before asking a question.

1. Here is example for FlexPWM (It is for different processor, but the module is the same)

Example MPC5604P FlexPWM Initialization on TRK board

2. Yes you can capture the PWM signal with FlexPWM or with eTimer.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, enwei

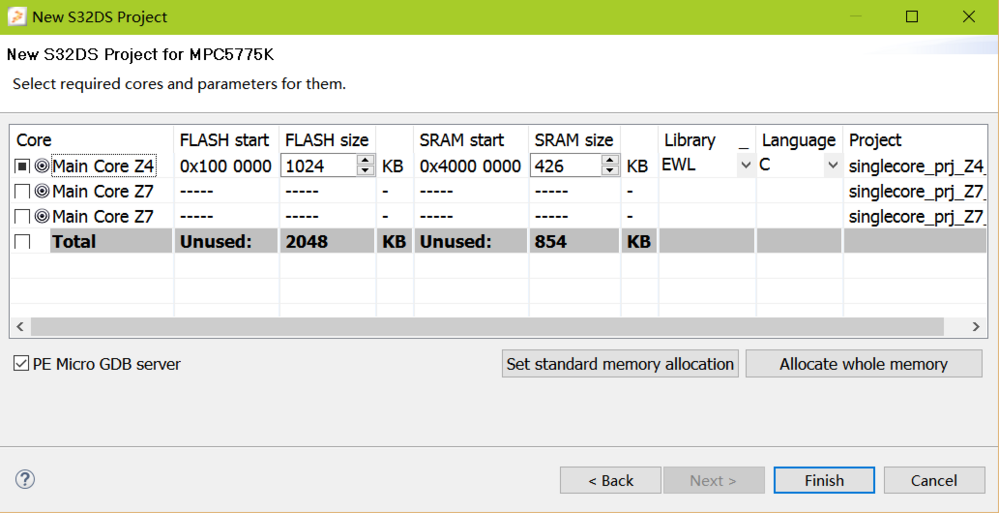

I found that the code below was able to work in a single core project. But if I create a new project in a multicore mode. The PWM would never generate the PWM. It was very strange. I don't know how to solve it.

Though there are three cores in the MCU, I only select one core. The FlexPWM module could work in the right way.

void PWMInit(void)

{

uint16_t val_x[4]={0,0,0,0};

SIUL2.MSCR[57].R = 0x02800001; // D[9] pin as FlexPWM X[0] output

//GPIO[57]

//PWM X0

FlexPWM_0.OUTEN.R = 0x001; // enable A,B and X outputs on submodule 0

FlexPWM_0.SUB[0].CTRL1.R = 0x0400; // full cycle reload, every opportunity,IPBus/1

FlexPWM_0.SUB[0].CTRL2.R = 0x2000; // independent pair operation

FlexPWM_0.SUB[0].DTCNT0.R = 0x0000; // deadtime values, not aplicable on INDEP mode

FlexPWM_0.SUB[0].DTCNT1.R = 0x0000;

FlexPWM_0.SUB[0].INIT.R = 0x0; // PWM init value

FlexPWM_0.SUB[0].VAL1.R = 13333; // PWM modulo, PWMX falling edge

FlexPWM_0.SUB[0].VAL0.R = 5000; // PWMX rising edge, half cycle reload point

FlexPWM_0.SUB[0].VAL2.R = 0; // PWM A0 rising edge

FlexPWM_0.SUB[0].VAL3.R = 0; // PWM A0 falling edge

FlexPWM_0.SUB[0].VAL4.R = 0; // PWM B0 rising edge

FlexPWM_0.SUB[0].VAL5.R = 0; // PWM B0 falling edge

FlexPWM_0.SUB[0].DISMAP.R = 0x0000; // disable fault pin condition

FlexPWM_0.SUB[0].DMAEN.R = 0x0200; // DMA write requests for VALx registers enabled

/* Load address of source data */

DMA.TCD[15].SADDR.R = (vuint32_t) &val_x[0];

/* Read 2 bytes per transfer */

DMA.TCD[15].ATTR.B.SSIZE = 1;

/* After transfer, add 2 to src addr */

DMA.TCD[15].SOFF.B.SOFF = 2;

/* After major loop, reset src addr */

DMA.TCD[15].SLAST.B.SLAST = - 8;

/* Source modulo feature not used */

DMA.TCD[15].ATTR.B.SMOD = 0;

/* Load address of destination */

DMA.TCD[15].DADDR.B.DADDR = (vuint32_t) &FlexPWM_0.SUB[0].VAL2.R;

/* Write 2 bytes per transfer */

DMA.TCD[15].ATTR.B.DSIZE = 1;

/* After transfer, add 2 to dest addr */

DMA.TCD[15].DOFF.B.DOFF = 2;

/* After major loop, reset dest addr */

DMA.TCD[15].DLASTSGA.B.DLASTSGA = - 8;

/* Destination modulo feature not used */

DMA.TCD[15].ATTR.B.DMOD = 0;

/* Transfer 8 bytes per minor loop */

DMA.TCD[15].NBYTES.MLNO.B.NBYTES = 8;

/* Initialize the begining and current major loop iteration counts */

DMA.TCD[15].BITER.ELINKNO.B.BITER = 1;

DMA.TCD[15].CITER.ELINKNO.B.CITER = 1;

DMA.TCD[15].BITER.ELINKNO.B.ELINK = 0;

DMA.TCD[15].CITER.ELINKNO.B.ELINK = 0;

DMA.TCD[15].CSR.B.DREQ = 0;

DMA.TCD[15].CSR.B.INTHALF = 0;

DMA.TCD[15].CSR.B.INTMAJOR = 0;

DMA.TCD[15].CSR.B.MAJORELINK = 0;

DMA.TCD[15].CSR.B.ESG = 0;

DMA.TCD[15].CSR.B.BWC = 0;

DMA.TCD[15].CSR.B.START = 0;

DMA.TCD[15].CSR.B.DONE = 0;

DMA.TCD[15].CSR.B.ACTIVE = 0;

DMA.ERQ.R = 0x00008000; // eDMA request signal for channel 15 is enabled

DMAMUX_0.CHCFG[15].R |= 0x8a; // route FlexPWM comp_val DMA request to eDMA channel 15

FlexPWM_0.MCTRL.B.RUN = 0x1; // Submodule 0 PWM generator enabled

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

Maybe it is necessary to describe all the details. I want to generate a configurable duty PWM in the FlexPWM module. And the output pin is X0. But I couldn't get the PWM . The below is my code sample. I don't know why it was not able to work. Could you correct it for me?

Thanks.

The MCU which I am working with is MPC 5775K.

The pin is GPIO[57], FlexPWM0 X0.

void RadarPWMInit(void)

{

//GPIO[57]

//PWM0 X0

SIUL2.MSCR[57].R = 0x02800001;

/* Submodule 0 Initialisation */

FlexPWM_0.OUTEN.B.PWMX_EN = 0x0001; // enable X outputs on submodule 0

FlexPWM_0.SUB[0].CTRL1.R = 0x0400; // full cycle reload, every opportunity,IPBus/1

FlexPWM_0.SUB[0].CTRL2.R = 0x2000; // independent pair operation

FlexPWM_0.SUB[0].DTCNT0.R = 0x0000; // deadtime values, not aplicable on INDEP mode

FlexPWM_0.SUB[0].DTCNT1.R = 0x0000; // deadtime

FlexPWM_0.SUB[0].INIT.R = 0x0; // PWM init value

FlexPWM_0.SUB[0].VAL0.R = 4096; // X

FlexPWM_0.SUB[0].VAL1.R = 1024; // X

FlexPWM_0.SUB[0].VAL2.R = 0;

FlexPWM_0.SUB[0].VAL3.R = 0;

FlexPWM_0.SUB[0].VAL4.R = 0;

FlexPWM_0.SUB[0].VAL5.R = 0;

FlexPWM_0.SUB[0].DISMAP.R = 0x0000;

// FlexPWM_0.SUB[0].DMAEN.R = 0x0200; // DMA write requests for VALx registers enabled

// FlexPWM_0.MCTRL.B.LDOK = 0x1; /* Load the PRSC bits of CTRL1 and the INIT, and VALx registers into a set of buffers */

FlexPWM_0.MCTRL.B.RUN = 0x1;

}