- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- LS1028A JTAG Interface Clarification

LS1028A JTAG Interface Clarification

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm in the process of implementing the JTAG interface to our LS1028A application. Figure 36 of the LS1028A Design Checklist (AN12028) shows a SPDT switch in an unconnected state with the following note:

2. This switch is included as a precaution for BSDL testing. The switch should be open during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, ensure this switch is closed.

The note does not mention which terminal it should be closed to. Should it be closed to the PORESET_B line or to the pull up to OVDD?

If it should be closed to a specific connection, what is the purpose or function for closing in the opposite direction?

We are also interested in interfacing the JTAG with another networking PHY device that has a JTAG port. That device has a TRSTn pin as an input that requires a pull down for normal operation. Figure 36 has a pull up for the input pin where other TRST_B sources would interface. Does this indicate the TRST interfaces of the networking PHY and LS1028A are incompatible, or does there just need to be a logic inverter?

Ideally, we would like to have a method where the switch is not being used due to the environment's vibration.

Figure 36 is attached.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) Yes, you are correct. One comment, "TRST is connected to PORESET" means TRST behaves as PORESET, not real mechanical/electrical contact.

2) I believe the PHY would be also ok with TRST high during normal operations if you assert it one time at/after power-up.

3) Yes, TRST can be held low on the LS1028A during normal operations. Designers said that this can add a bit more power consumption, but do not specify how much.

Regards,

Bulat

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Bulat ,

I have few queries regarding same topic -:

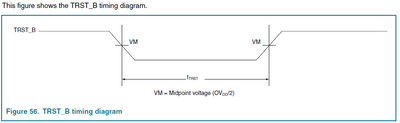

1) TRST_B signal has a timing requirement as stated by Processor's datasheet as shown below. Who shall provide TRST_B with the given timing?

2) Is there any timing relation between PORESET_B and TRST_B ?

3) If we have an option to dismiss the usage of the logical gate, where shall the nRESET from Codewarrior to be connected ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

To confirm:

- For normal operation, TRST is connected to PORESET

- For JTAG testing, TRST must be logic high and independent of PORESET, including boundary scan

Is this correct?

I'm also looking at integrating a networking PHY with a JTAG interface into this system. That datasheet says the following regarding TRST.

"JTAG Reset. TRSTn pin requires a 4.7 kΩ pull-down externally for normal operation"

Are these requirements compatible? Can TRST just be held low during all normal operation, then high during JTAG testing? If so, would a simple fixed pull down on this pin suffice, then use a jumper to pull up for testing in a lab or manufacturing environment?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) Yes, you are correct. One comment, "TRST is connected to PORESET" means TRST behaves as PORESET, not real mechanical/electrical contact.

2) I believe the PHY would be also ok with TRST high during normal operations if you assert it one time at/after power-up.

3) Yes, TRST can be held low on the LS1028A during normal operations. Designers said that this can add a bit more power consumption, but do not specify how much.

Regards,

Bulat

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Bulat, thank you again for the response.

For now, I have decided to omit the PHY JTAG connection and just implement the LS1028A JTAG. Your information has been helpful, and I will mark the first response as the resolution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The figure does not mean that the user has to use a mechanical switch, logic-based circuit is fine. Normally it assumes TRST is connected to PORESET signal, this would assert TRST alone with PORESET each power up cycle to reset TAP logic. However if the user runs boundary scan test, such a connection is not allowed. PORESET is a 1149.1 compliance enable pin and must be '0' during JTAG testing, while TRST must not be '0' that time. So external logic should provide these simple rules depending on mode of operations: normal flow or boundary scan.

Regards,

Bulat