- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- LPC55S69 : GINT0 and GINT1

LPC55S69 : GINT0 and GINT1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC55S69 : GINT0 and GINT1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello !

Do I understand right and any GPIO pin from group 0 or 1 can be included to GINT0 or 1.

So the same pin can't be in both GINTx but it port 0 pins can be part of GINT1 and vise versa.

Is this so.

But if I select edge sensitivity of all pins what are part of GINT0 group, can I select falling edge or rising edge

for each pin individually or for all of them ?

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Eugene Hiihtaja,

" any GPIO pin from group 0 or 1 can be included to GINT0 or 1."

-> Yes, any pins from PORT0 and PORT1 can be included to GINT0 and 1.

" the same pin can't be in both GINTx but it port 0 pins can be part of GINT1 and vise versa."

-> I think the same pin can be in both GINT0 and 1.

"

can I select falling edge or rising edge

for each pin individually or for all of them

"

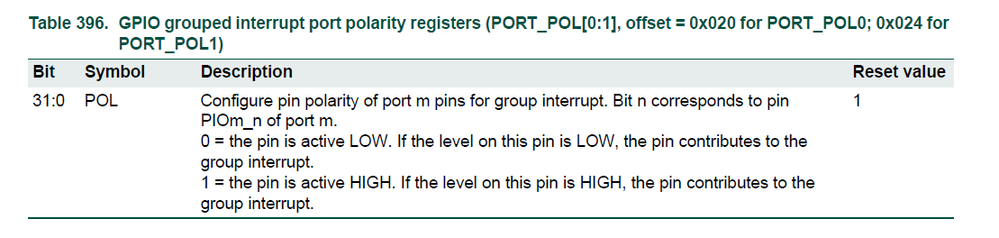

-> Yes, you can config them individually. The PORT_POL register can config each pin polarity:

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alice !

It means I should include pin to both group if I would like to detect both edges.

Is this so ?

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

YES.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alice !

For some reason it dosn't work like this. Please look y request : LPC55S69 : GINTx, detect both edges

If one pin is included to both GINTx it works, but if more, only falling edge starts to work.

May be special powermanagement API should be called ?

But for me it is blocker.

I need to find out reason and see if ISP,SW2,SW3 on EVK can be programmed in way that all edges are detected for 3 pins at list.

Can https://community.nxp.com/thread/517579 be prioritized some how ?

Regards,

Eugene

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Eugene,

There will other people help you on that thread.