- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- LCDIF 8bits bus-width interface to 24 bits LCD display on IMX6UL

LCDIF 8bits bus-width interface to 24 bits LCD display on IMX6UL

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am currently working with the imx6ul and I need to configure the mxsfb driver that supports the eLCDIF controller to enable the use of 8 bits bus-width with 24 bits RGB pixels.

My configuration is:

- imx6Ultralite,

- LCD 320x240 24 bits RGB display connected to the first LCD_DATA pins (0-7),

- tested with the 24 bits bus-width and it is working fine

- DOTCLK mode is used (HSYNC + VSYNC + DATA ENABLE) and NOT MPU 8080 or i80.

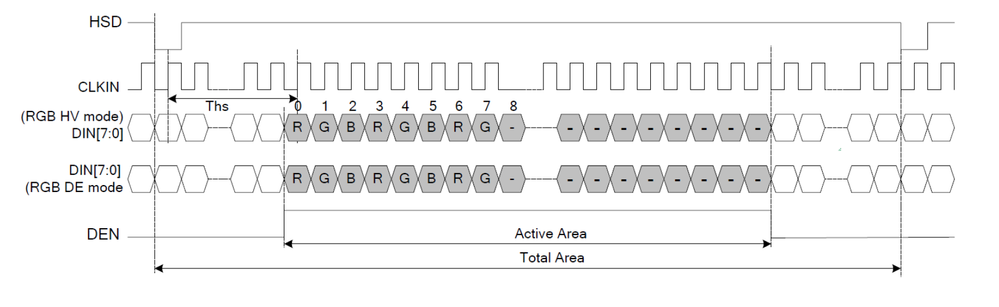

The current driver supports the 24 bits pixels to 24 bits bus-width but as shown in the image hereafter, the 8 bits mode of the display requires to output R, G and B on the same LCD pins one after the other. In order to do that, the LCD display needed PXL_CLK increases from 6 MHz to 26 MHz.

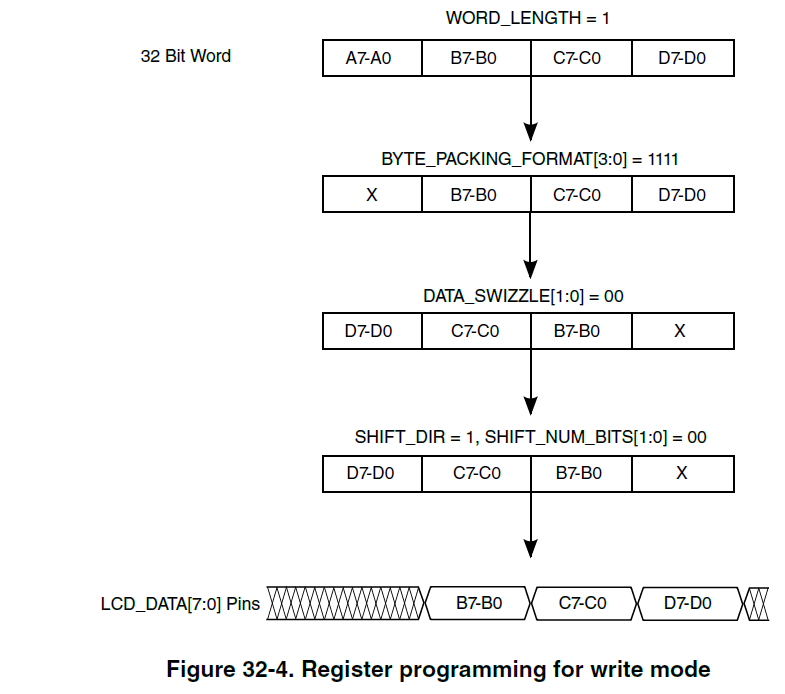

I increased the PXL_CLK directly in the CCM to 26 MHz and configured the register of the eLCDIF with the following values:

Any help with a guidance towards which register should be modified to make it works ?

Thank you !

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi henri_koch

one can try to set "bus-width" to 8 in dts file [&lcdif..] and adjust "display-timings" according to

lcd datasheet:

imx6ul-14x14-evk.dts\dts\boot\arm\arch - linux-imx - i.MX Linux kernel

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi henri_koch

one can try to set "bus-width" to 8 in dts file [&lcdif..] and adjust "display-timings" according to

lcd datasheet:

imx6ul-14x14-evk.dts\dts\boot\arm\arch - linux-imx - i.MX Linux kernel

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------