- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- RTC stops working in VLLS1 unless OSCERCLK is enabled

RTC stops working in VLLS1 unless OSCERCLK is enabled

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

RTC stops working in VLLS1 unless OSCERCLK is enabled

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

I am developing a battery backed-up application with MKL36Z256VLL4 where the device enters VLLS1 when mains power is not available and wakes up as soon as mains power is available again. Power to MCU is supplied from the battery when there is no mains.

A 32-kHz crystal is connected to oscillator pins and the MCU runs at ~48 MHz during normal RUN mode. I am using FEE mode for MCG configuration. RTC clock source is selected as OSC32KCLK in SIM_SOPT1 register and works fine during RUN mode.

The device must keep date and time during RUN mode and VLLS1 mode. I am able make MCU to enter and exit VLLS1 successfully. Since it is a battery powered application I want to reduce sleep current as much as possible. To do this I want to turn off OSCERCLK before entering VLLS1. According to reference manual this should not harm RTC operation since RTC clock source is selected as OSC32KCLK in SIM_SOPT1 register and this clock source is not derived from OSCERCLK.

In order to keep RTC running during VLLS1, oscillator is kept ON (ERCLKEN = 1) always. However when EREFSTEN bit in OSCx_CR register is cleared before entering VLLS1, RTC stops working (time does not increment) until the MCU wakes up and reconfigures the oscillator with EREFSTEN = 1. If I do not clear EREFSTEN before entering VLLS1, RTC keeps track of time well during VLLS1 but this results in an increased sleep current.

What am I missing? How can I turn off OSCERCLK in VLLS1 mode while keeping the RTC run?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Beware that the LPO is not very accurate and so the RTC will tend to drift by maybe 5 minutes an hour, which makes it unsuitable for precision time keeping.

See also this report and recommendation about the RTC in the KL parts:

http://www.utasker.com/kinetis/KL_RTC.html

RTC and time keeping: http://www.utasker.com/docs/uTasker/uTasker_Time.pdf

Regards

Mark

Complete Kinetis solutions for professional needs, training and support: http://www.utasker.com/kinetis.html

uTasker: supporting >1'000 registered Kinetis users get products faster and cheaper to market

Request Free emergency remote desk-top consulting at http://www.utasker.com/services.html

Open Source version at https://github.com/uTasker/uTasker-Kinetis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Mark,

Using LPO is not an option due our accuracy constraints. So I have to use OSC32KCLK in all modes.

The problem is with the EREFSTEN bit not with ERCLKEN. During VLLS1 I want to get rid of OSCERCLK not ERCLK32K. Since ERCLK32K is not derived from OSCERCLK, turning off OSCERCLK should be ok and RTC should be working fine in VLLS1. However that's not the case.

How can I turn off OSCERCLK in VLLS1 mode while keeping the RTC run?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

As discussed in the report, the crystal oscillator circuit is not operational in very low power modes and therefore you need to add an external low power oscillator to RTC_CLK in order to keep track of time accurately.

The other option is to change to a part which has a dedicated RTC oscillator and VBAT.

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark,

I do not think that the information in the report is correct since I can run RTC from OSC32KCLK during VLLS1 mode and confirm that the time keeps tracking when the device is in RUN mode again as long as I do not clear EREFSTEN bit before entering VLLS1.

You can also check table 7.1 of reference manual where it says:

"VLLS1 (VeryLow-LeakageStop1)

• Most peripherals are disabled (with clocks stopped), but OSC, LLWU, LPTMR, RTC, CMP, TSI, LCD can be used.

• NVIC is disabled; LLWU is used to wake up.

• All of SRAM_U and SRAM_L are powered off. The 32-byte system register file remains powered for customer-critical data."

Also please check table 7.2 where it states that System oscillator (OSC) operation is limited to low range/low power in VLLS1/3 and OFF in VLLS0.

By the way my oscillator is configured as low range low power.

From these I understand that OSC can be kept alive during VLLS1, am I correct?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Orhan

I agree with you that the report is not correct in this case since the RTC is usable in VLLS1 when a 32kHz crystal is available. [The report concentrates on Freedom boards with LCD and high frequency crystal and needs to be extended].

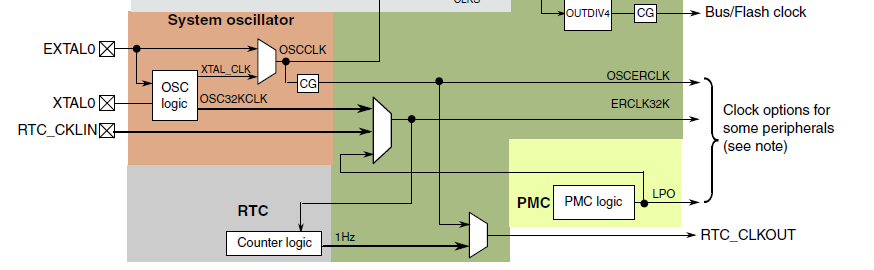

From the block diagrams given in the user's manual it does look like it should be possible to disable OSCERCLK without disturbing the RTC but if practical tests show otherwise it may be that the diagrams are not fully accurate or it may be that there is a chip errata (check the errata to your chip to be sure).

Do you achieve current consumption according to the values in the data sheet or are you above them at the moment?

Regards

Mark

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mark,

I already checked chip errata however could not find any reported issue about this problem.We are trying to increase battery (CR2032 - 150 mAh) lifetime as much as possible so every micro ampere is a catch :smileyhappy:

I wrote to NXP FAE and waiting for a response from him as well.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Orhan

My FRDM-KL46Z board (super-set of, and compatible with KL36) has a 16MHz oscillator so I couldn't test the case on this but instead I tested on the FRDM-KL43Z. This doesn't have the same clock module but the board has a 32kHz crystal and the oscillator/RTC part is the same:

I run the CPU from the IRC48M and use the system oscillator as 32kHz exclusively for the RTC.

My results are the same as yours.

As long as OSC_CR is set to 0xa0 (oscillator enabled and OSCERCLK runs in stop mode) the RTC will continue counting in low power modes (VLLS1 for example). As soon as OSC_CR is changed to 0x80 (enabled but OSCERCLK stops in low power modes) the RTC freezes when in the low power state.

The exception is VLLS0, where the RTC always freezes, irrespective of the OSC_CR value: this is expected since it is stated so in the user's manual.

Therefore my conclusion is, based on your reports with the KL36 and my tests with the KL43, is that the RTC freezes when OSCERCLK is stopped in STOP modes (including VLLS1) which is not expected according to the block diagram. The block diagram suggests that the RTC can continue to run from OSC32KCLK when OSCERCLK is stopped but this seems not to be the case when controlled by the OSC directly.

HOWEVER if the RTC_CR is configured to control the OSC via its OSCE bit (CLKO can also be set to 1 so that it doesn't supply the clock to other peripherals) OSC_CR can be left at 0.

Now the RTC continues counting in VLLS1.

I don't have a multi-meter with me at the moment (being on holiday with just a few basic boards to work with) so I can't confirm that the current is lower like this than the OSC_CR = 0xa0 setup. But you can try the same with your KL36 board (it has the same RTC registers) so see whether it does represent a way to stop the maximum internal peripheral clocks while allowing RTC operation in VLLS1 (and various other low power modes).

That is, try OSC_CR = 0; and RTC_CR = 0x300; instead of OSC_CR = 0xa0; and see whether it gives you better low current performance or not!

Good luck!

Regards

Mark

Complete Kinetis solutions for professional needs, training and support: http://www.utasker.com/kinetis.html

Kinetis KL25, KL26, KL27, KL28, KL43, KL46, KL82

- http://http://www.utasker.com/kinetis/FRDM-KL25Z.html

- http://www.utasker.com/kinetis/TWR-KL25Z48M.html

- http://www.utasker.com/kinetis/FRDM-KL26Z.html

- http://www.utasker.com/kinetis/TEENSY_LC.html

- http://www.utasker.com/kinetis/FRDM-KL27Z.html

- http://www.utasker.com/kinetis/Capuccino-KL27.html

- http://www.utasker.com/kinetis/FRDM-KL28Z.html

- http://www.utasker.com/kinetis/FRDM-KL43Z.html

- http://www.utasker.com/kinetis/TWR-KL43Z48M.html

- http://www.utasker.com/kinetis/FRDM-KL46Z.html

- http://www.utasker.com/kinetis/TWR-KL46Z48M.html

- http://www.utasker.com/kinetis/FRDM-KL82Z.html

uTasker: supporting >1'000 registered Kinetis users get products faster and cheaper to market

Request Free emergency remote desk-top consulting at http://www.utasker.com/services.html

Open Source version at https://github.com/uTasker/uTasker-Kinetis

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Orhan,

If you check in the next section of the reference manual, you will see that the RTC needs a clock source to operate:

I think you're using the OSC32KCLK and as the page 118 says, the external clock will be disabled:

I think if you change the source of the RTC and enable the LPO before enter VLLS1, the RTC will continue operating.

I hope this helps you.

Best Regards,

Alexis Andalon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Alexis,

As you mentioned I use OSC32KCLK as RTC clock source and keep ERCLKEN always set in order to guarantee proper RTC operation in all modes.

The problem is with the EREFSTEN bit not with ERCLKEN. During VLLS1 I want to get rid of OSCERCLK not ERCLK32K. Since ERCLK32K is not derived from OSCERCLK, turning off OSCERCLK should be ok and RTC should be working fine in VLLS1. However that's not the case.

How can I turn off OSCERCLK in VLLS1 mode while keeping the RTC run?