- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- Product Forums

- :

- S32K

- :

- S32K144 -Conflict in PORTA PIN5 CFG vs RESET signal

S32K144 -Conflict in PORTA PIN5 CFG vs RESET signal

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there.

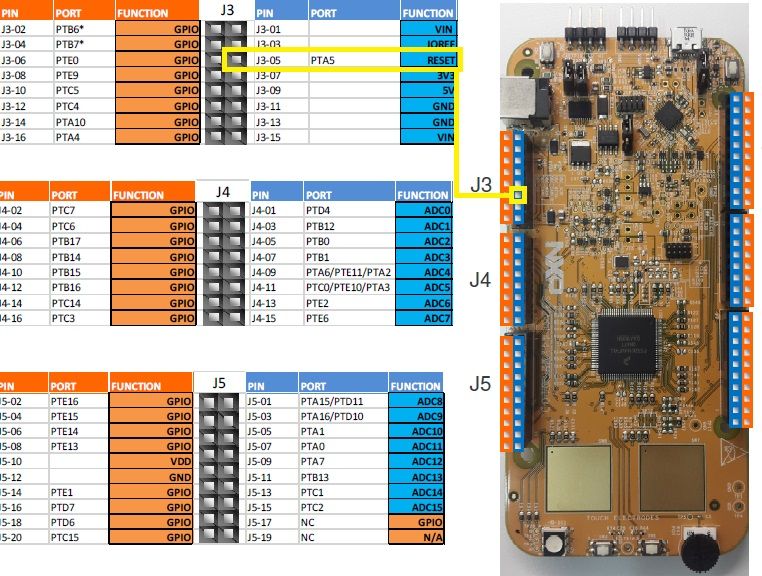

I'm working with the evaluation board "S32K144 _EVB - Q100".

I'm performing an integration of the SDK drivers examples within a project (drivers are provided in the S32DS installation folder, I did some modifications but mainly they are the same).

The tool chain used is:

- Compiler + Linker IAR for ARM for the executable building.

- IAR EWB configured with a SEJJER J-Link interface (ultra+).

- SEGGER JLINK Flasher for download the executable without debugging.

After the latest change I did on the IO ports configuration something strange happen:

The microcontroller seems to be completely inaccessible from the DEBUG and the FLASHER.

However the SW inside the the microcontroller works.

After some investigation seems that the RESET port is just like inhibited.

If I generate a reset pulse on the uC pin the SW keep to work.

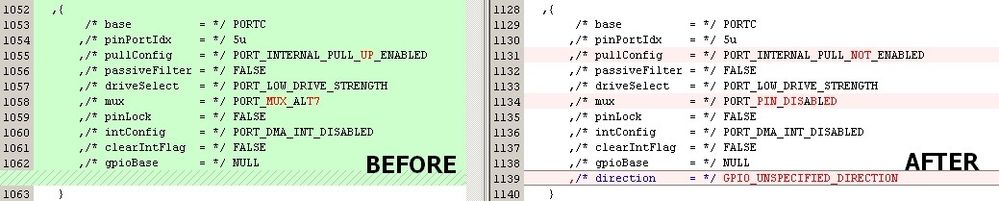

The change I did seems to be related somehow to the RESET pin configuration: see below...

The configuration structure is re-adaptation (for my project) of the "pin_settings_config_t" that I found in an SDK example.

That configuration affects the PORTA PIN5 connected to the RESET of the EVB: see below...

I've got a couple of questions:

- Is this microcontroller provided with a feature which inhibit the reset function via SW configuration?

- If yes...How can I get back from this situation? Because the debugger is not even able to communicate with the micro.

Thanks in advance.

BR.

A.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, the PTA5 reset pin can be reconfigured for alternative functions. The reset function is the default one, so you need to reset the device. Since you cannot use that pin to restart the MCU, you need to connect to the MCU after power-on-reset in the short time window before it gets reprogrammed again.

P&E has a recovery utility that tries to halt the execution during the start-up sequence.

Please refer to Bricking and Recovering FRDM-KL25Z Boards: Reset, SWD Clock and Low Power

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, the PTA5 reset pin can be reconfigured for alternative functions. The reset function is the default one, so you need to reset the device. Since you cannot use that pin to restart the MCU, you need to connect to the MCU after power-on-reset in the short time window before it gets reprogrammed again.

P&E has a recovery utility that tries to halt the execution during the start-up sequence.

Please refer to Bricking and Recovering FRDM-KL25Z Boards: Reset, SWD Clock and Low Power

Regards,

Daniel