- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5xxx, Internal Flash Erase/Write a Privileged operation?

MPC5xxx, Internal Flash Erase/Write a Privileged operation?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5xxx, Internal Flash Erase/Write a Privileged operation?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are developing a boot utility for loading internal Flash with a MPC5554. Our Flash Programming utilities are working as long as the processor is running in Privilege Mode (MSR.PR = 0). But, if we switch to User Mode (MSR.PR = 1) the processor crashes (exceptions and finally a reset). Indications are that things begin going wrong when either the Erase or Write functions start to write to the Flash registers:

- Flash_MCR (16 #C3F8_8000#)

- Flash_HLR (16 #C3F8_8000#)

- Flash_HSR (16 #C3F8_8000#)

Our debug environment is not particularly reliable when the processor is in User Mode so I hesitate to get into the details of the failure. Depending on my test code I have seen Machine Check and Program-Privilege Exceptions. But, they might not have been the first exception.

I am concerned that the Flash Register memory space (C3F8xxxx) is considered a “privileged resource”. This would not surprise me considering what the registers control. But, I did not find anything in the documentation that specifically said it. Can anyone confirm this is/isn’t the case?

If it helps we are using the following definition for the TLB for that memory space:

MAS1 |

|

reserved-0 | 0 (0x0) |

Selected TLB (must be 1) | TLBSEL_ (0x1) |

reserved-0 | 0 (0x0) |

Enytry select for TLB1 | ESEL_ (0x0) |

reserved-0 | 0 (0x0) |

Next replacement victim | NV_ (0x0) |

MAS2 |

|

Valid | VALID_Y (0x1) |

Invalidation protect | IPROT_Y (0x1) |

reserved-0 | 0 (0x0) |

Translation ID | TID_ (0x0) |

reserved-0 | 0 (0x0) |

Translation Address space | TS_ (0x0) |

Entry page size | TSIZE_1M (0x5) |

reserved-0 | 0 (0x0) |

MAS3 |

|

Effective page number | 0x0C3F00 |

reserved-0 | 0 (0x0) |

Write Through | W_N (0x0) |

Cache Inhibited | I_Y (0x1) |

Memory coherence (ignored) | M_N (0x0) |

Guarded (ignored) | G_Y (0x1) |

Little Endian | E_N (0x0) |

MAS4 |

|

Real Page Number | 0x0C3F00 |

reserved-0 | 0 (0x0) |

User bit 0 | U0_N (0x0) |

User bit 1 | U1_N (0x0) |

User bit 2 | U2_N (0x0) |

User bit 3 | U3_N (0x0) |

User Execute | UX_Y (0x1) |

Supervisor Execute | SX_Y (0x1) |

User Write | UW_Y (0x1) |

Supervisor Write | SW_Y (0x1) |

User Read | UR_Y (0x1) |

Supervisor Read | SR_Y (0x1) |

|

|

Any assistance would be appreciated. If you can point me to the area of the documentation that supports your ideas, that would be really appreciated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

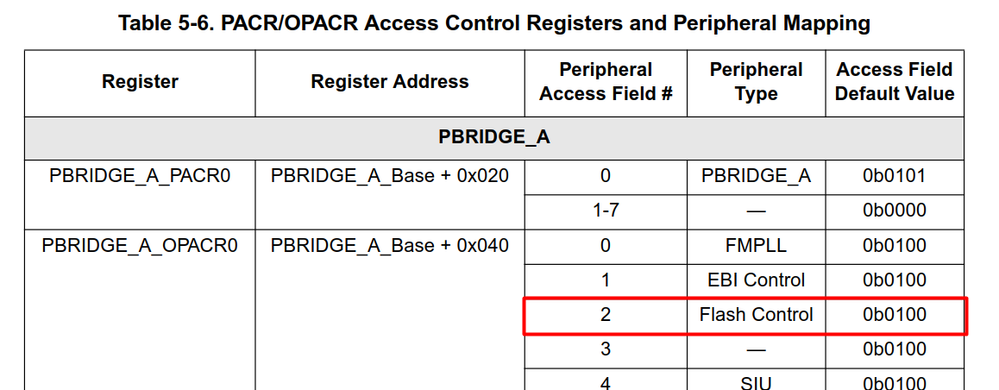

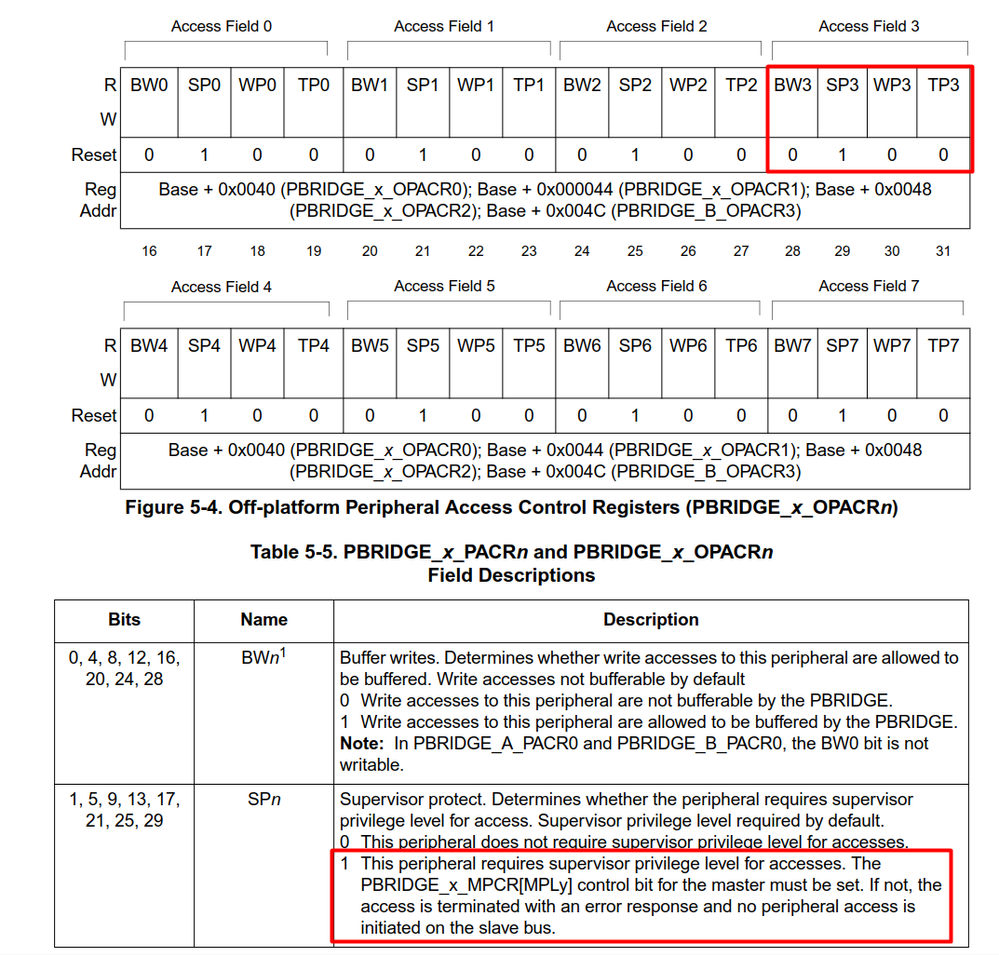

Hi, I don't think flash registers would require supervisor mode, but if you default setting of PBRIDGE, it requires such access for flash registers. Pay attention to screenshots below:

Hope it helps