- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- P-Series

- :

- P1020RDB-PD TDM tests and issues

P1020RDB-PD TDM tests and issues

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

P1020RDB-PD TDM tests and issues

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In reference to the other thread:

TDM Driver Working in Internal Loopback mode During Validation

The document within it TDM Driver Working in Internal Loopback mode During Validation.pdf

described changes to the TDM driver more specifically

changing

#define TDM_CLK_DIV_VAL 0x85

to

#define TDM_CLK_DIV_VAL 0xC3

within TDM_FSL.c

In that previous thread I have pointed out that first of all the TDM_LOOPBACK_TEST.c

algorithm had major issue and was actually failing 99% of the time...

That test was fixed up ( algorithmwise ) and it was shown to be PASSing for P1010RDB

Under further scrutiny my findings are:

Looking/reviewing again the test logs/results that you performed back in January using P1010 show that you were using

external clock... I would like to see you rerun your tests using internal clock on P1010 and see that you a get positive results...

Since you were using external clock the value of 0xC3 for TDM_CLK_DIV_VAL was not even used...

I am using P1020RDB-PD

the TDM_TEST.c with the DTMF loopback and the freshly updated TDM_LOOPBACK_TEST.c are performing OK

as long as I am using the external clock...

if I use within TDM_FSL.c the following line

dev_node = of_find_compatible_node( NULL, NULL, "fsl,P1020RDB-PD" );

to force P1020 to use internal clock... then both of above tests are FAILing...

I have tried these tests with each of the below values with not much luck...

#define TDM_CLK_DIV_VAL 0x85

#define TDM_CLK_DIV_VAL 0xC3

Can you please run above tests on P1020RDB-PD using internal clock

and let me know what TDM_CLK_DIV_VAL should be set to...

and if there is any hope for these tests to PASS using INTERNAL CLOCK...

Thanks,

Naum Grutman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Naum,

Please refer to the following update from the AE team, would you please also provide more information about a question from them?

<AE Team>:

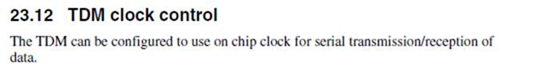

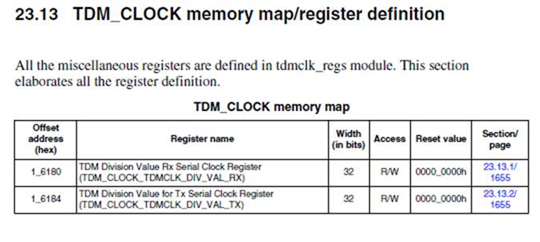

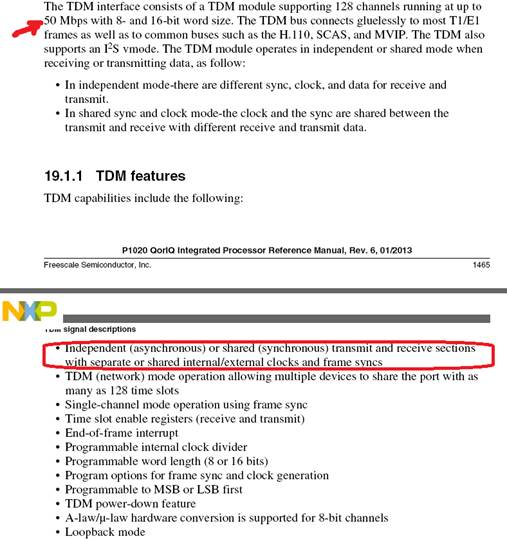

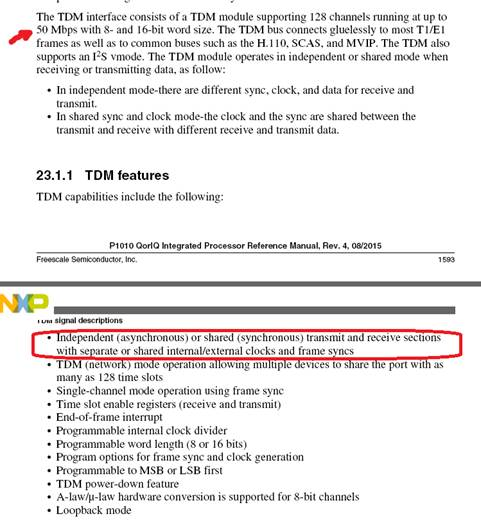

We looked at the Ref Manuals of P1020, P1010 and T1040. There is a section of TDM Clock control <see snips below, It is there in P1010RM and T1040RM but NOT in P1020RM

So a question to understand the customer requirement better:

What is the customer looking for? I mean will they be using this in their product as a feature? Or it is being used by them for some validation purpose?

Meanwhile we are looking for some person in design team to check if these registers are there in P1020 or not.And also try to get the validation/verification status of this feature.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yipping

Please find answers to yours and/or AE’s questions:

What is the customer looking for?

-> We are in the process of building a product that is gonna be very much

depending on P1020’s TDM and its abilities and capabilities…

I mean will they be using this in their product as a feature?

-> Yes, we will be using TDM in our product extensively

and need for P1020 to produce 10Mbps clock on the TDM

It clearly states that 50Mbps should be handled…

We are just looking for 1/5 of that 10Mbps

Or it is being used by them for some validation purpose?

-> Obviously, currently we are trying to validate above

that is why we are using the P1020RDB product and are looking for

TDM_LOOPBACK_TEST to PASS using Internal clock

And also want Internal clock configured correctly

to produce 10Mbps bit clock on the TDM

I have provided excerpts for P1020 and P1010 Reference manuals

Obviously you can see that they offer same TDM features.

We definitely want all the TDM features listed on P1020

and have TDM validated via TDM_LOOPBACK_TEST

using internal clock configured to produce 10Mbps

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Naum Grutman,

Please refer to the following information which I got from our hardware team.

P1010 and P1020 are different devices, with different silicon inside, so TDM function is not guaranteed to be identical.

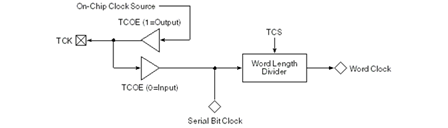

For P1010: This is a copy of Figure 23-7 from P1010 Reference Manual:

You can see “On-Chip Clock Source” and gate controller by TCOE bit (this bit is in TDM_SB_TDMTIR register, see Section 23.5.3)

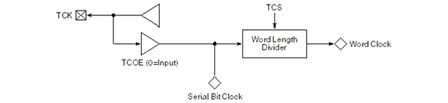

Now similar Figure from P1020 Manual – Figure 19-37:

No “On-Chip Clock Source” path and no TCOE bit. The same in TDM_SB_TDMTIR register – bit 22 is reserved.

So – yes, P1020 TDM block is different in regards to internal clock, according to P1020 Reference Manual.

In addition, probably we need to do further discussion about what you are doing now, actually this should not be public in the community, this should be private as normal. So I suggest you create a ticket(case) from Sales and Support|NXP to describe your current problem in details. Your Ticket will be addressed in our internal system, you will get timely reply through email from our TIC support team. The email is sent out from "NXP Technical Support", if you reply to this email, your update will be addressed in our system automatically.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Naum Grutman,

I have created a case 00110698 in our internal tickets tracking system as a copy of this thread, we could continue to discuss your current problem in that case. Because what we are going to discuss is about the designing of your company's products, so we should not continue to discuss in the community thread publicly to paste everything here.

Yesterday, I reminded you to use internal tickets(cases) to discuss your problems instead of making everything public in community, probably you are not familiar with the process of internal cases creation, so I created case 00110698 from our internal system and sent email out to you.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yiping,

I have a question a question about TDM on P1020

I have the TDM working just fine on within Linux and trying to make it it work within vxWorks

I have put together the the TDM driver for vxWorks based on the Linux driver within your SDK and also based on P1020 QorIQ Reference Manual Rev.6 page# 1519

I do steps 1 thru 4 and based on item number 5 I have to read the TSR and RSR and wait for those to get on...

but they never do... Could you shed some light on this subject...

- Bring the chip out of reset.

- Program the TDM control registers-TDM RIR, TDM RFP, TDM TIR, TDM TFP,

and TDM GIR.

- Program all channel enable registers (TDM RCENn , TDM TCENn ) and transmit

channel mask registers (TDM TCMAn ) as disabled.

- Enable the TDM Rx and Tx by setting the TDM RCR[REN] and TDM TCR[TEN]

bits.

- Wait until TDM TSR[TENS] and TDM RSR[RENS] are set.

- If the TDM is serviced by:

- DMA transfer-immediately use a software started DMA channel to write data to

the Tx data register(s) (must be completed before two Tx frame syncs arrive

after enabling).

- Interrupts-immediately write data to the Tx data register(s) (must be completed

before two Tx frame syncs arrive after enabling).

- Follow the steps outlined in Dynamic channel configuration while TDM operating-shared,

to enable channels.

- All other writes and reads will be initiated by either an interrupt or a DMA request,

depending on the configuration.

On Linux TDM TSR and TDM RSR do get set

====================================

F519A000: 00000001 0000E241 0000E041 007F0030 .......A...A...0

F519A010: 007F0030 007F0030 007F0030 007F0030 ...0...0...0...0

F519A020: FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF ................

F519A030: FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF ................

F519A040: FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF ................

F519A050: FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF ................

F519A060: 00000000 00000000 00000000 00000000 ................

F519A070: 00000000 00000000 00000000 00000000 ................

F519A080: 00000001 00000001 00000000 00000000 ................

F519A090: 00000000 00000000 00000000 00000000 ................

F519A0A0: 000001C0 000001C0 00000005 00000025 ...............%

On vxWorks instead of TSR and RSR I get 0x00000001 in Reserved fields marked in RED

==========================================================================

F3016000: 00000001 0000E241 0000E041 007F0030 .......A...A...0

F3016010: 007F0030 007F0030 007F0030 007F0030 ...0...0...0...0

F3016020: FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF ................

F3016030: FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF ................

F3016040: FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF ................

F3016050: FFFFFFFF FFFFFFFF FFFFFFFF FFFFFFFF ................

F3016060: 00000000 00000000 00000000 00000000 ................

F3016070: 00000000 00000000 00000000 00000000 ................

F3016080: 00000001 00000001 00000000 00000000 ................

F3016090: 00000001 00000001 00000001 00000001 ................

F30160A0: 00000000 00000000 00000000 00000000 ................

Could you shed some light on this subject...

Thanks,

Naum

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Naum Grutman,

Thank you for your detailed information, we need to contact the processor design team to do further confirmation regarding TDM internal clock feature on P1020, will give you feedback as soon as possible.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yipping

Please find answers to yours and/or AE’s questions:

What is the customer looking for?

-> We are in the process of building a product that is gonna be very much

depending on P1020’s TDM and its abilities and capabilities…

I mean will they be using this in their product as a feature?

-> Yes, we will be using TDM in our product extensively

and need for P1020 to produce 10Mbps clock on the TDM

It clearly states that 50Mbps should be handled…

We are just looking for 1/5 of that 10Mbps

Or it is being used by them for some validation purpose?

-> Obviously, currently we are trying to validate above

that is why we are using the P1020RDB product and are looking for

TDM_LOOPBACK_TEST to PASS using Internal clock

And also want Internal clock configured correctly

to produce 10Mbps bit clock on the TDM

I have provided excerpts for P1020 and P1010 Reference manuals

Obviously you can see that they offer same TDM features.

We definitely want all the TDM features listed on P1020

and have TDM validated via TDM_LOOPBACK_TEST

using internal clock configured to produce 10Mbps

<http://www.rugged.com/>

Naum Grutman

Tel: ( 818 ) 700-2000 Ext. 163

Fax: ( 818 ) 407-1502

Address: 19756 Prairie St. Chatsworth, CA.91311

E-mail: ngrutman@rugged.com<mailto:ngrutman@rugged.com>

Website: www.rugged.com<http://www.rugged.com/>;

Embedded Computing without Compromise

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have reported this issue with the following thread:

https://community.nxp.com/docs/DOC-333351

TDM Driver Working in Internal Loopback mode During Validation

since the issue is related and is on the same subject etc... etc...

but I have been asked to create a new thread... so I have done that...

P1020RDB-PD TDM tests and issues

Would anybody please look into this issue...

Thanks,

Naum

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Naum,

Please refer to the attached tdm source file and test log on T020RDB-PD board.

For using the external clock, please configure the following in the driver file tdm/device/tdm_fsl.c.

static int tdm_internal_clk = 0;

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yiping,

1. Is INTERNAL CLOCK available on P1020RDB ???

2. Can this parameter "TDM_CLK_DIV_VAL" be used ?

If the answer to above is YES and YES then

Please show me that the highlighted code below executes and test is PASSing….!!!!!!!

if (tdm_internal_clk) {

//out_be32(&priv->tdm_regs->rir,

// RIR_RFWM(RIR_RFWM_VAL) | RIR_RFEN | RIR_RWEN | RIR_RDMA |

// RIR_RSO | RIR_RCOE | RIR_RRDO | RIR_RFSD(RIR_RFSD_VAL));

//out_be32(&priv->tdm_regs->tir,

// TIR_TFWM(TIR_RFWM_VAL) | TIR_TFEN | TIR_TWEN | TIR_TDMA |

// TIR_TCOE | TIR_TSL | TIR_TSO | TIR_TRDO |

// TIR_TFSD(TIR_RFSD_VAL));

out_be32(&priv->tdm_regs->rir,

RIR_RFWM(RIR_RFWM_VAL) | RIR_RFEN | RIR_RWEN | RIR_RSO | RIR_RCOE |

RIR_RDMA | RIR_RFSD(RIR_RFSD_VAL) | RIR_RRDO);

out_be32(&priv->tdm_regs->tir,

TIR_TFWM(TIR_RFWM_VAL) | TIR_TFEN | TIR_TWEN | TIR_TSO | TIR_TCOE |

TIR_TDMA | TIR_TFSD(TIR_RFSD_VAL) | TIR_TRDO);

out_be32(&priv->clk_regs->tx, TDM_CLK_DIV_VAL);

out_be32(&priv->clk_regs->rx, TDM_CLK_DIV_VAL);

pr_info("TDM configured to use internal clock");

} else {

/*

Rx Water mark 0, FIFO enable, Wide fifo, DMA enable for RX,

Receive Sync out, syncwidth = ch width, Rx clk out,zero sync,

falling edge , data order

*/

out_be32(&priv->tdm_regs->rir,

RIR_RFWM(RIR_RFWM_VAL) | RIR_RFEN | RIR_RWEN | RIR_RDMA |

RIR_RSL | RIR_RSO | RIR_RCOE | RIR_RRDO |

RIR_RFSD(RIR_RFSD_VAL));

out_be32(&priv->tdm_regs->tir,

TIR_TFWM(TIR_RFWM_VAL) | TIR_TFEN | TIR_TWEN | TIR_TDMA |

TIR_TSL | TIR_TSO | TIR_TRDO | TIR_TFSD(TIR_RFSD_VAL));

pr_info("TDM configured to use external clock");

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Naum,

I also got failed result on P1020RDB for the internal clock testing.

It seems that TDM_CLK_DIV_VAL value is not correct for P1020, I need to do more investigation, will give you feedback later.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yiping,

Now,

that you finally agree with me… and see for yourself that TDM_LOOPBACK_TEST

is FAILing using internal clock… please respond to our requirements for P1020…!!!

We need to see that this TDM_LOOPBACK_TEST is gonna PASS

using TDM_CLK_DIV_VAL that will produce 10MHz bit clock on the TDM

So again the following TWO STEPS are essential for us…!!!

- What is the TDM_CLK_DIV_VAL that will produce10MHz bit clock on the TDM…???

- And to see the PASSing results for TDM_LOOPBACK_TEST with TDM_CLK_DIV_VAL

from above Step 1 applied…

Thanks again,

Naum

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Naum,

I just verified the TDM internal clock loopback testing on P1010RDB-PB, it passed without any problem.

When run the internal clock testing code on P1020RDB-PD, the TDM channel cannot receive any data, I am afraid the internal clock mode is not supported by P1020, because I cannot find these registers TDM_CLOCK_TDMCLK_DIV_VAL_RX/TDM_CLOCK_TDMCLK_DIV_VAL_TX definition in P1020 Reference Manual at all, at least this testing code working in internal clock mode is not suitable for P1020.

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yiping,

I would like to see the current log file showing that you have TDM_P1010

PASSing the TDM_LOOPBACK_TEST under Internal Clock....!!!!

and its TDM_CLK_DIV_VAL value...!!!

Please attach it to your response... !!!

Thanks,

Naum

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Naum,

I searched from our internal Data base today, found a service request on 5/23/2012, it states "The internal clocking mechanism of TDM was de-featured in P1020".

Anyway, I am still waiting for the authoritative confirmation from USA hardware AE team, will give you more update later.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Naum,

Please refer to the attached source code, dts and testing log for P1010RDB-PB platform.

You could find "TDM configured to use internal clock" in the console log.

I am not sure whether TDM internal clock mode is support on P1020RDB-PD and how to decide TDM Division Value for P1020, I have confirmed with the hardware AE team, am still waiting for the feedback.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Naum,

According to the information which I provided previously, indeed TDM internal clock mode loopback test succeed on P1010RDB-PB, but failed on P1020RDB-PD, I have made many test on this issue these days. I also contacted one of the TDM driver author, but this driver was designed 7 years ago, he couldn't remember much. I also asked for the hardware AE team to confirm TDM hardware on P1020RDB-PD still am waiting for for the result.

This morning the factory team informed me that your issue had been escalated to them, they are investigating your problem parallel.

I will still keep tracking this issue, if I have any outcome or get any feedback from AE team, I will let you know in my first time.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yiping,

Now,

that you finally agree with me… and see for yourself that TDM_LOOPBACK_TEST

is FAILing using internal clock… please respond to our requirements for P1020…!!!

We need to see that this TDM_LOOPBACK_TEST is gonna PASS

using TDM_CLK_DIV_VAL that will produce 10MHz bit clock on the TDM

So again the following TWO STEPS are essential for us…!!!

1. What is the TDM_CLK_DIV_VAL that will produce10MHz bit clock on the TDM…???

2. And to see the PASSing results for TDM_LOOPBACK_TEST with TDM_CLK_DIV_VAL

from above Step 1 applied…

Thanks again,

<http://www.rugged.com/>

Naum Grutman

Tel: ( 818 ) 700-2000 Ext. 163

Fax: ( 818 ) 407-1502

Address: 19756 Prairie St. Chatsworth, CA.91311

E-mail: ngrutman@rugged.com<mailto:ngrutman@rugged.com>

Website: www.rugged.com<http://www.rugged.com/>;

Embedded Computing without Compromise

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Naum,

We are very sorry we overlooked this issue, Yiping is a bit overloaded this week.

Yiping is now working on your question and will reply you as early as she can. We will take this issue with highest priority.

Have a great day,

Jennie Zhang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yiping,

Please show me that the highlighted code below executes and test is PASSing….!!!!!!!

if (tdm_internal_clk) {

//out_be32(&priv->tdm_regs->rir,

// RIR_RFWM(RIR_RFWM_VAL) | RIR_RFEN | RIR_RWEN | RIR_RDMA |

// RIR_RSO | RIR_RCOE | RIR_RRDO | RIR_RFSD(RIR_RFSD_VAL));

//out_be32(&priv->tdm_regs->tir,

// TIR_TFWM(TIR_RFWM_VAL) | TIR_TFEN | TIR_TWEN | TIR_TDMA |

// TIR_TCOE | TIR_TSL | TIR_TSO | TIR_TRDO |

// TIR_TFSD(TIR_RFSD_VAL));

out_be32(&priv->tdm_regs->rir,

RIR_RFWM(RIR_RFWM_VAL) | RIR_RFEN | RIR_RWEN | RIR_RSO | RIR_RCOE |

RIR_RDMA | RIR_RFSD(RIR_RFSD_VAL) | RIR_RRDO);

out_be32(&priv->tdm_regs->tir,

TIR_TFWM(TIR_RFWM_VAL) | TIR_TFEN | TIR_TWEN | TIR_TSO | TIR_TCOE |

TIR_TDMA | TIR_TFSD(TIR_RFSD_VAL) | TIR_TRDO);

out_be32(&priv->clk_regs->tx, TDM_CLK_DIV_VAL);

out_be32(&priv->clk_regs->rx, TDM_CLK_DIV_VAL);

pr_info("TDM configured to use internal clock");

} else {

/*

Rx Water mark 0, FIFO enable, Wide fifo, DMA enable for RX,

Receive Sync out, syncwidth = ch width, Rx clk out,zero sync,

falling edge , data order

*/

out_be32(&priv->tdm_regs->rir,

RIR_RFWM(RIR_RFWM_VAL) | RIR_RFEN | RIR_RWEN | RIR_RDMA |

RIR_RSL | RIR_RSO | RIR_RCOE | RIR_RRDO |

RIR_RFSD(RIR_RFSD_VAL));

out_be32(&priv->tdm_regs->tir,

TIR_TFWM(TIR_RFWM_VAL) | TIR_TFEN | TIR_TWEN | TIR_TDMA |

TIR_TSL | TIR_TSO | TIR_TRDO | TIR_TFSD(TIR_RFSD_VAL));

pr_info("TDM configured to use external clock");

}

<http://www.rugged.com/>

Naum Grutman

Tel: ( 818 ) 700-2000 Ext. 163

Fax: ( 818 ) 407-1502

Address: 19756 Prairie St. Chatsworth, CA.91311

E-mail: ngrutman@rugged.com<mailto:ngrutman@rugged.com>

Website: www.rugged.com<http://www.rugged.com/>;

Embedded Computing without Compromise