- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5643L_some details about CTU FIFO and DMA

MPC5643L_some details about CTU FIFO and DMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

About CTU FIFO

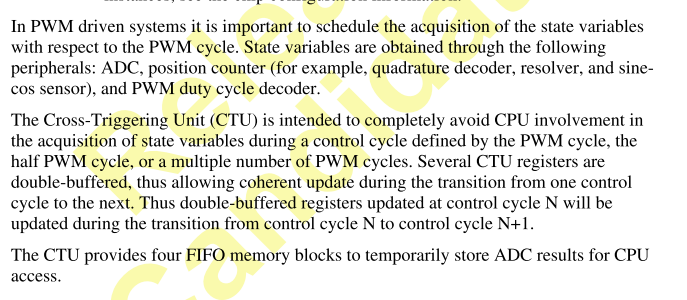

Q1: I want to use CTU trigger send a command to ADC, then use FIFO 0 overflow event trigger a DMA transfer. I feel unsure about the FIFO 0 threthold value. For example:

IF FIFO 0 threthold equals 4, how many ATD results when FIFO 0 contains will cause a DMA transfer, 4 or 5 ?

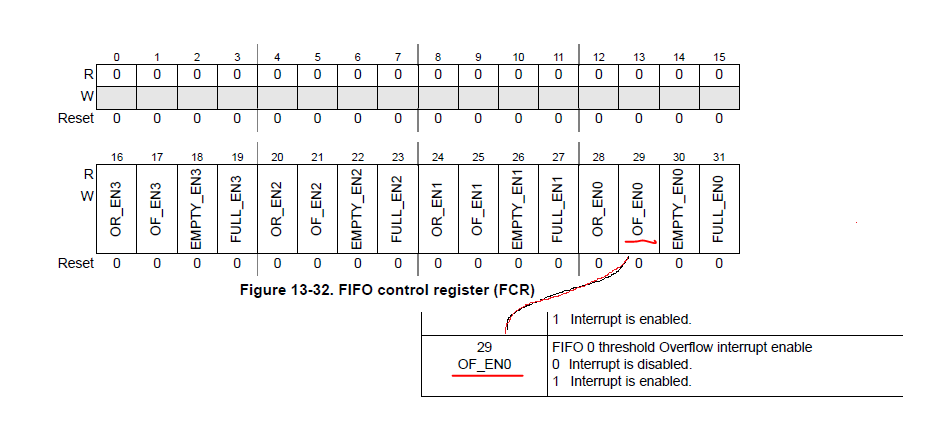

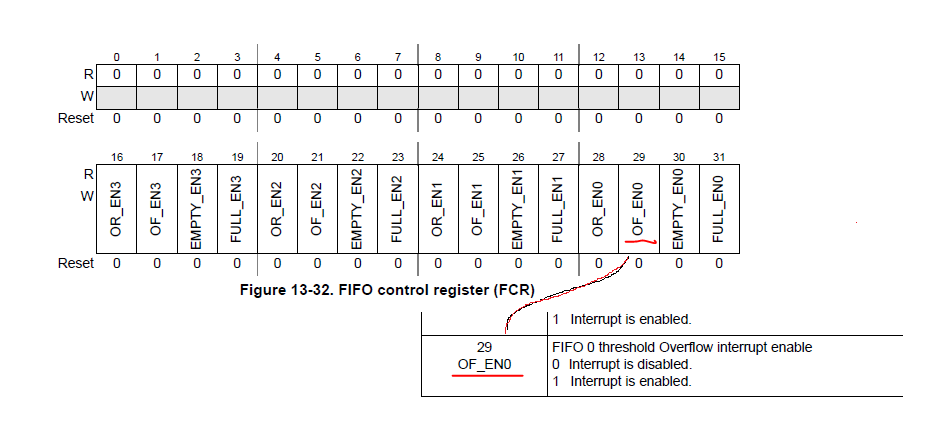

Q2: I cann’t quite understand the FIFO control register,for example: FIFO 0 overflow interrupt enable bit .

From the corresponding codes of MPC5643L technical support (PWM triggered measurement concept) written by Peter Vina and AN4797 by Yves Briant ,we get know that they both use FIFO 0 overflow event trigger a DMA transfer. What’s the relationship between the event and FIFO 0 overflow interrupt enable bit which they both set?

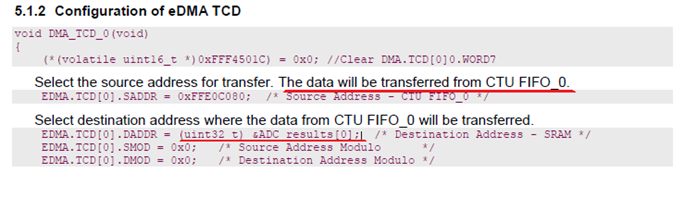

Following code is from the technical support by Peter Vina.

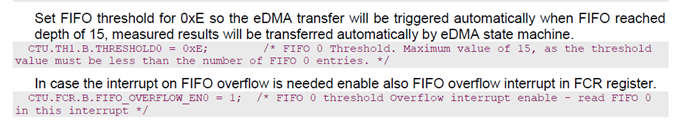

CTU.TH1.B.THRESHOLD0 = 0xE; /* FIFO 0 Threshold. Maximum value of 15, as the threshold value must be less than the

number of FIFO 0 entries. */

CTU.FCR.B.FIFO_OVERFLOW_EN0 = 1; /* FIFO 0 threshold Overflow interrupt enable - read FIFO 0 in this nterrupt */

I think we only need to configure the corresponding DMA enable bit for FIFO 0 bit and DMA channel source, isn’t it right? Why we need to configure FIFO 0 overflow interrupt enable bit ?

Such as CTU.FDCR.R = 0x1; // Enable DMA for FIFO0

DMAMUX.CHCONFIG[5].B.SOURCE = 8; // CTU FIFO0 threshold

Thanks very much!

Yanna

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

1. you don't have to enable FIFO interrupt.

2. If you enable DMA transfer then it is done on FIFO threshold.

In my application FIFO depth is 15 (0 to 15), the number of ADC results in FIFO is 16 (this means depth 15 as FIFO starts from FIFO_0).

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

A3:

Each submodule can request a DMA read access for its capture FIFOs and a DMA write request for its double buffered SUBn_VALx registers.

You completely misunderstood the usage of this feature.

It is desired for update of double buffered VALx registers. For example is you wan to generate continuous duty cycle increase from 0% to 100%. The DMA transfer is triggered when Reload flag is set!

Make sure you read the reference manual before asking a questions. All these information are there.

If you require training on MPC5643L peripheries do not hesitate to order one.

A4: Configure your DMA to do so, if you want to avoid CPU intervention. No special sample code is needed, just configure DMA to transfer bytes you want to.

A5: Yes SW interrupts are drawing you computational power of CPU. Also a time critical motor control applications benefits from CTU/DMA.

CTU is there to support accurate and fast measurements for high speed motor applications. But all this is in reference manual!

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

1. you don't have to enable FIFO interrupt.

2. If you enable DMA transfer then it is done on FIFO threshold.

In my application FIFO depth is 15 (0 to 15), the number of ADC results in FIFO is 16 (this means depth 15 as FIFO starts from FIFO_0).

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Q5: Hi,Peter.

I think you may only want to explain how to use FlexPWM and CTU and eDMA module in your application.

In practical application,did a FIFO DMA transfer without CPU intervention have a great advantage

over a FIFO interrupt with CPU intervention ?

For example:

In your application,you transfer the data with a DMA request.

Also it can use FIFO 0 interrupt event to tranfer data,such as FIFO 0 overflow interrupt

First,enable the FIFO 0 interrupt

(CTU.FCR.B.FIFO_OVERFLOW_EN0 = 1; /* FIFO 0 threshold Overflow interrupt enable)

Second,write the FIFO_0 overflow isr code

void FIFO_0 overflow isr(void)

{

ADC_results[0]= CTU.FRA[0].R // or ADC_results[0]=ADC.CDRx.R

…

}

Did transfering the data from FIFO 0 to ADC_results[0] through FIFO 0 interrupt cost much time? How long it will cost? (CTU.FRA[0].R contains 16 bit data )

I think a DMA transfer have a great advantage when the transfer data was array which contains many data.

Thanks very much!

Yanna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

About FIFO DMA request and FIFO interrupt

Q4: Hi,peter

In your application,the data was transferred from CTU FIFO 0 to the address &ADC_results[0] .

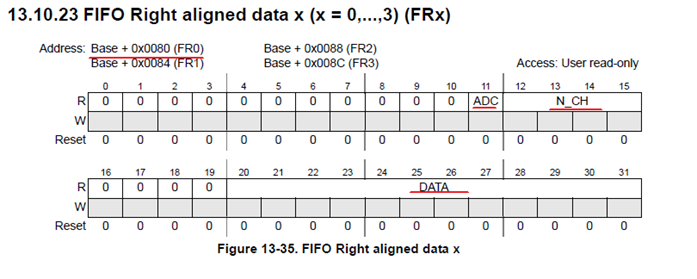

We know the value in the FIFO 0 not only include the data we need but also the information about the ADC

unit and channel.

We often get the data using the sentence like temp=ADC_results &&0FFF.

Did there exist another method to get the result only include the data(no ADC unit and channel information)

from the source address? Did there exist sample codes?

Thanks very much!

Yanna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,Peter

Thanks very much! I have got it.

could you help me for another two question above?

Thanks very much!

Yanna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

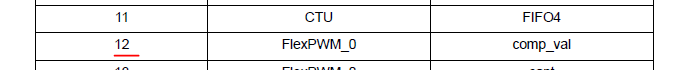

About DMA_MUX source comp_val source

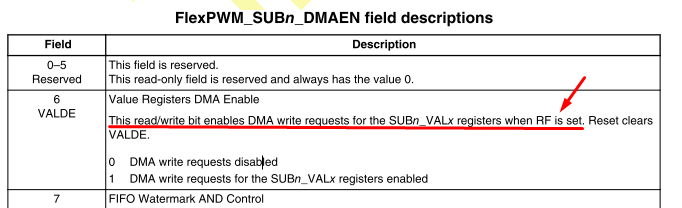

Q3:If I want to use FlexPWM0_sub0 valx write DMA request,then I need to configure corresspoding register, like

FLEXPWM_0.SUB[0].DMAEN.B.VALDE = 1; //Enable DMA

DMAMUX.CHCONFIG[1].B.SOURCE = 12; //FlexPWM write request

so when the counter reach the value of VALx(x=0,1,2,3,4,5),a DMA transfer will occur,is it right?

Is it possible a DMA transfer occur only when the counter reach the value of VAL0 not included other VALx(x=0,2,3,4,5)? Did there exist the register which select the VALx write request to the comp_val signal?

Thanks very much!

Yanna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I recommend you to have a look on my application example:

MPC5643L PWM_ADC measurement concept

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,Peter

My understanding is the FIFO interrupt enable bit needn’t be configured when we need use FIFO DMA request event.

1. Your applitation configure FIFO interrupt enable bit directly without explaination.

We read FIFO through a DMA transfer, not interrupt.

2. Your applitation set FIFO threthold for 0XE, my understanding is when FIFO contains 16 ATD results ,

a DMA transfer will occur.But in your applitation,you said FIFO reached depth of 15, I think it should be 16.

is my understanding wrong?

3. Only question 1 and 2 have relation with your applitation, the other two haven’t.

Thanks very much!

Yanna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

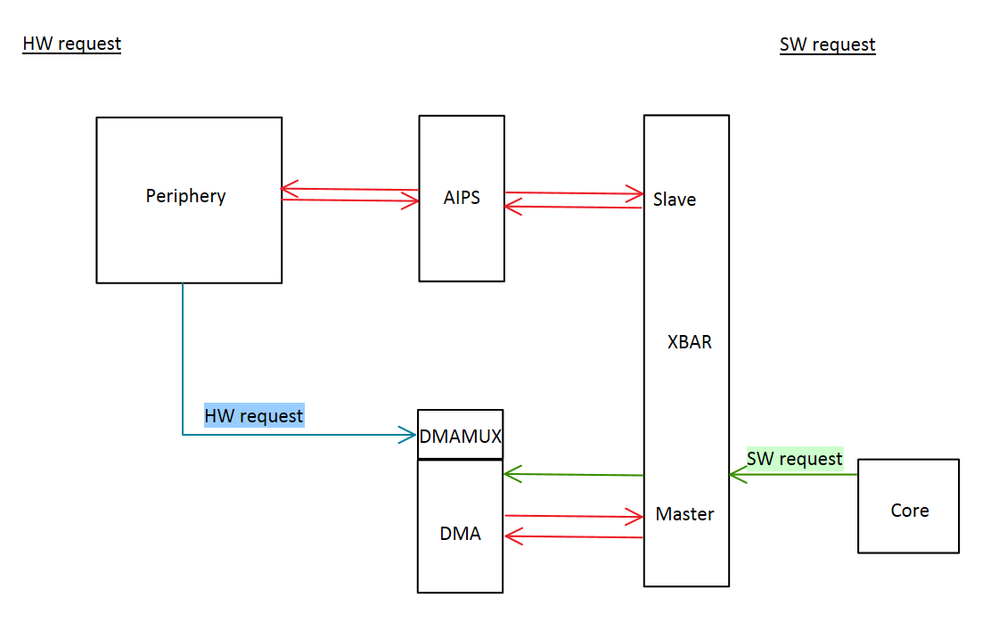

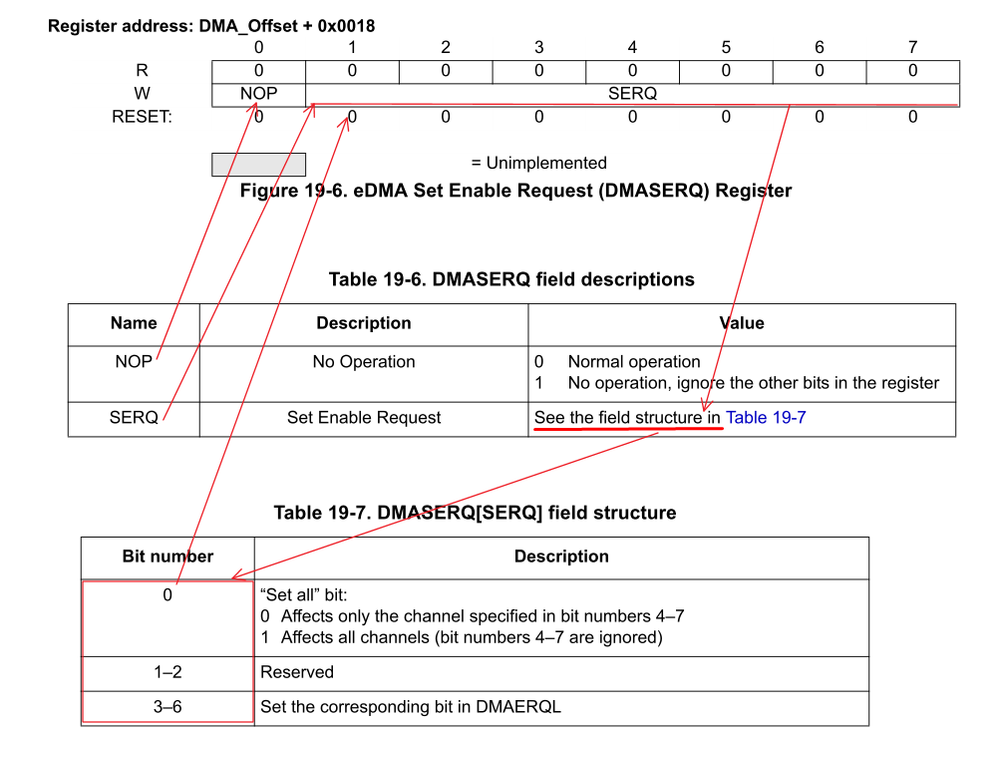

About DMASERQ register

First,I want to verify whether my understanding about the channel service request is right.

Channel service requests include hardware service request and software request and channel linking request.

hardware service request is from DMA peripheral sources ,

software request is determined by TCD.start bit,

if we use a channel’s hardware service request,we should configure correspoding DMA_MUX channel source and enable request bit(DMAERQL or DMASERQ). However ,if we use software request and channel linking request,we needn’t to configure corresponding enable bit, is it right?

I think there may exist typos in page 408 of RM.

Thanks very much!

Yanna

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1.Right. See my drawing.

If you use SW request you needn't to configure DMA mux. In case of HW request you must configure DMA MUX.

2. There is no typo in RM. But the description is little confusing. I hope that following picture will bring the light to the problematic.

Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,Peter.

Thanks very much! Your explanation is very clear .

Table 19-7 describes the structure of DMASERQ[SERQ] field, not DMASERQ.

I’m sorry for my carelessness.

Looking forward to your reply about question3&4&5(Q3&Q4&Q5) below.

Thanks very much!

Yanna