- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Hi, I'd like to clock a bunch of peripherals from a common clock source, to generate some complex synchronized waveforms. Peripherals of interest include FlexIO2, FlexPWM, LPSPI, QTIMER.

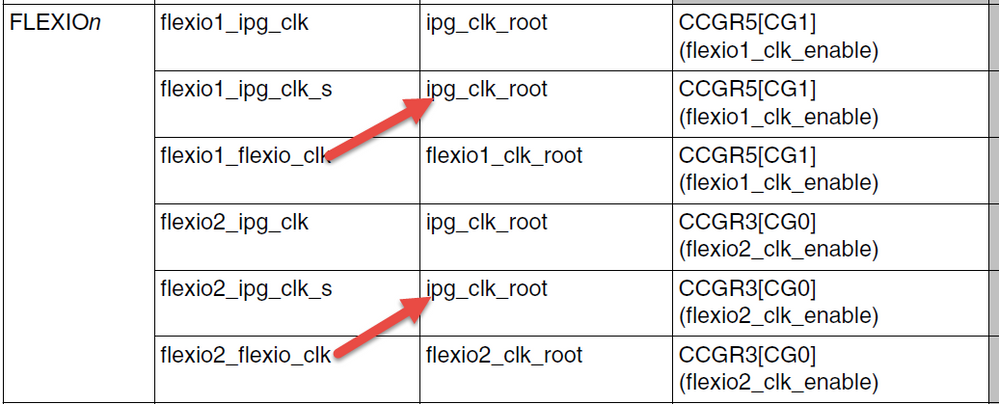

Reference Manual Rev 4, Table 14-4 (System Clocks, Gating and Override) suggests that I could use ipg_clock_root for all of these peripherals. I've searched the RM, but can't find any way to switch say FLEXIO2 from FLEXIO2_CLK_ROOT to IPG_CLK_ROOT.

Is this possible, and if so, how do I go about doing it?

I'd appreciate any hints.

Thanks

Eamonn

已解决! 转到解答。

Eamonn

The FLEXIO2_CLK_ROOT is used for bus accesses and so is probably not relevant for synchronisation of peripherals (as long as fast enough to allow other clocks to be recognised).

A possibility is to output IPG_CLK_ROOT on a CLKO pin and feed that to a FlexIO (clock) input pin so that its functionality is then synchronised to the same clock source as used by other peripherals.

Regards

Mark

[uTasker project developer for Kinetis and i.MX RT]

Hi Eamonn Heffernan,

Thank you for your interest in NXP Semiconductor products and

for the opportunity to serve you.

I'm not very clear with your question, whether you change the root clock of the XXXX_flexio_clk from the XXXX_clk_roor to ipg_clk_root.

If yes, I'm afraid it's impossible.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Jeremy,

To be clear, I would like to change the root clock of FlexIO2 from flexio2_clk_root to ipg_clk_root, as the RM seems to suggest. I need to use the same clock for a few different peripherals. If it's impossible, why does the RM suggest that it is possible? What does Table 14-4 mean? Why is ipg_clk_root mentioned if it cannot be used?

Thank you very much for taking the time to look at this issue.

Best - Eamonn

Eamonn

The FLEXIO2_CLK_ROOT is used for bus accesses and so is probably not relevant for synchronisation of peripherals (as long as fast enough to allow other clocks to be recognised).

A possibility is to output IPG_CLK_ROOT on a CLKO pin and feed that to a FlexIO (clock) input pin so that its functionality is then synchronised to the same clock source as used by other peripherals.

Regards

Mark

[uTasker project developer for Kinetis and i.MX RT]

Mark Butcher wrote:

A possibility is to output IPG_CLK_ROOT on a CLKO pin and feed that to a FlexIO (clock) input pin so that its functionality is then synchronised to the same clock source as used by other peripherals.

Great idea, Mark. I'll look into this. Thank you very much.

-Eamonn