- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: i.MX RT eLCDIF RGB Mode Use Case

i.MX RT eLCDIF RGB Mode Use Case

I have run the evkmimxrt1060_elcdif_rgb example on my imx RT1060 dev board. Then I modified it based on this doc so that I can run the demo on a 1280x800 LCD: https://www.nxp.com/docs/en/application-note/AN12302.pdf

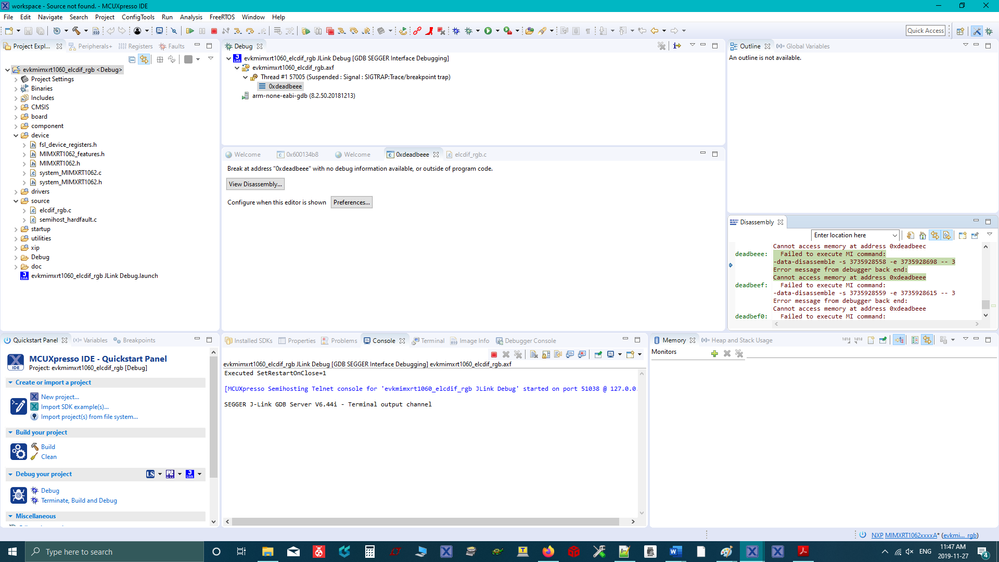

after the modifications I did I get this message:

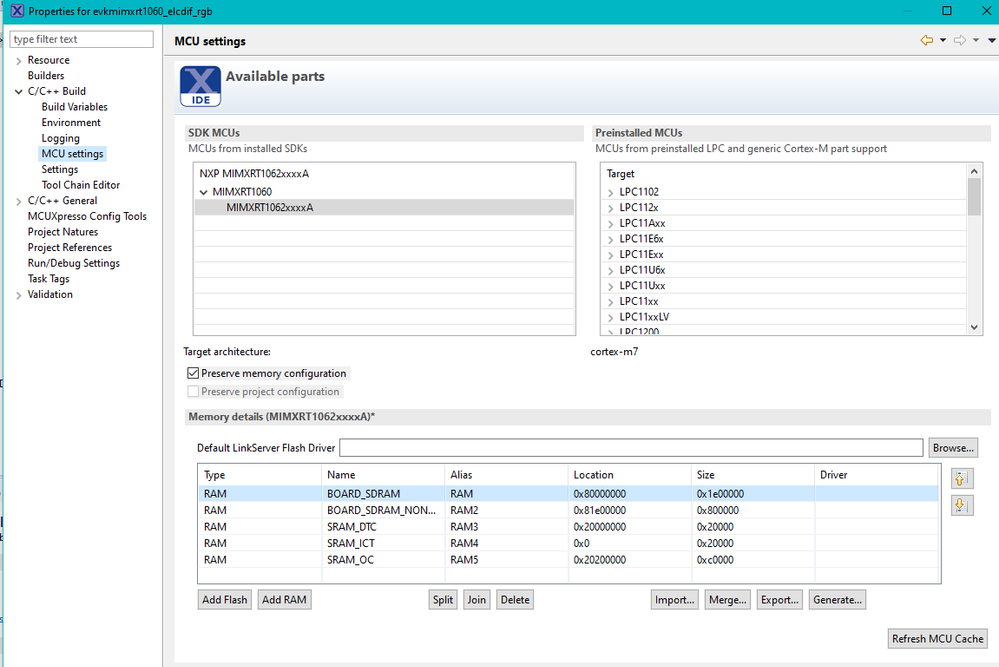

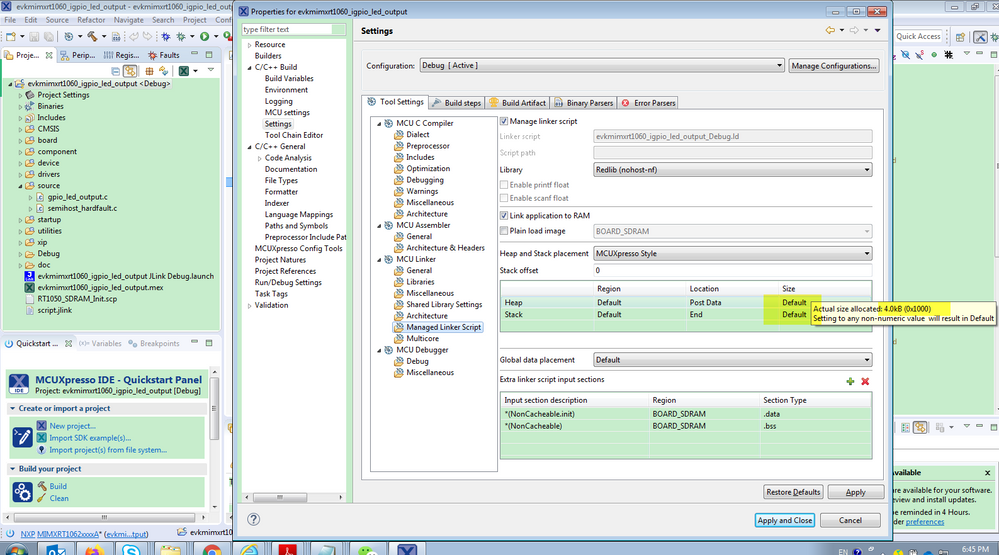

This is how I configured my memory:

已解决! 转到解答。

Hi Andre marcus,

Thanks for your updated information.

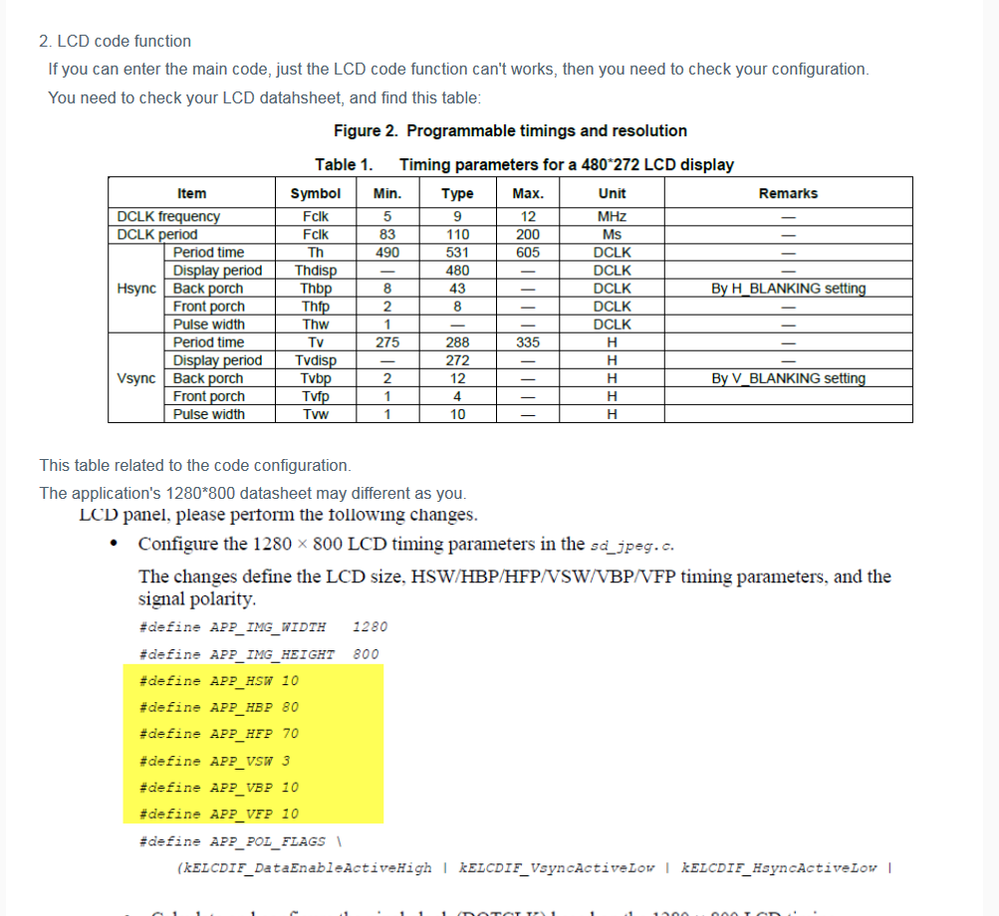

If you can't meet the target of 60 frames per seconds, it is still related to the HSW, HBP, HFP, VSW, VBP, VFP data of your LCD, I find you are totally use the application note data, but you didn't refer to your own LCD datasheet data.

In fact, I can't find the HSW, HBP, HFP, VSW, VBP, VFP data in the LCD file which you have shared.

Still as my reply in the previous time:

You need to find your own LCD controller related data, then define it in the code, and calculate the related video PLL output clock, and configure it in your project.

Wish it helps you!

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

My LCD is 1280x800 and it does not need Vsync and Hsync. It only uses DE ( data enable.)

The issue I’m having now is that I can’t meet the target of 15 frames per second even if I’m using 16 bits color depth pixel.

How can I optimize my eLCDIF speed so that I can have 15 frames/second. The frame buffers are stored in 8MB non-cacheable SDRAM.

Thank you in advance for your help!

I figured out how to set the master bit, please see below:

void APP_ELCDIF_Init(void)

{

const elcdif_rgb_mode_config_t config = {

.panelWidth = APP_IMG_WIDTH,

.panelHeight = APP_IMG_HEIGHT,

.hsw = APP_HSW,

.hfp = APP_HFP,

.hbp = APP_HBP,

.vsw = APP_VSW,

.vfp = APP_VFP,

.vbp = APP_VBP,

.polarityFlags = APP_POL_FLAGS,

//.bufferAddr = (uint32_t)s_frameBuffer[0],

.bufferAddr = (uint32_t)BframeBuffer,

.pixelFormat = kELCDIF_PixelFormatXRGB8888,

.dataBus = APP_LCDIF_DATA_BUS,

};

ELCDIF_RgbModeInit(APP_ELCDIF, &config);

APP_ELCDIF->CTRL|= 1<<5 ;

APP_ELCDIF->CTRL2 = 0x00700000;

}

Any comments?

Hi Kerry! I checked with the lcd manufacturer and found that vsync and Hsync signals need to be pulled low or set to logic low. How can I change these pins yo logic low. I’m assuming once the eLCDIF peripheral is initialized, these signals will be pulled up high. How do I make sure vsync and Hsync are pulled low at all times?

Thanks

Hi Andre marcus,

Do you mean, the vsync and hsync signals, need to be always low in your LCD? if yes, you don't need to configure the related RT code to these pins, you can connect your HSYNC and VSYNC pins in the LCD directly to the GND.

Best Regards,

Kerry

1. I don't think I set master bit to 1; how do I do that, and which register is it?

2. Could you please let me know how you guys configure the pixel clock. I took the example of generating a frequency of 70.5 MHz as it is, but I need to now how did this turn out to be the case when you used these clock functions:

/* * 000 derive clock from PLL2 * 001 derive clock from PLL3 PFD3 * 010 derive clock from PLL5 * 011 derive clock from PLL2 PFD0 * 100 derive clock from PLL2 PFD1 * 101 derive clock from PLL3 PFD1 */ CLOCK_SetMux(kCLOCK_LcdifPreMux, 2); CLOCK_SetDiv(kCLOCK_LcdifPreDiv, 0); CLOCK_SetDiv(kCLOCK_LcdifDiv, 0);

3. is there any limitation of the selection of posdivider, and loop divider below?

/ * Initialize the Video PLL. * Video PLL output clock is OSC24M * (loopDivider + (denominator / numerator)) / postDivider = 70.5MHz. */ clock_video_pll_config_t config = { .loopDivider = 47, .postDivider = 16, .numerator = 0, .denominator = 0, };

I will make sure I will get the HSW, HBP, HFP, VSW, VBP, VFP from the LCD maker. In the meantime, can you tell me if I memcpy() function instead of the nested for loop would make any difference?

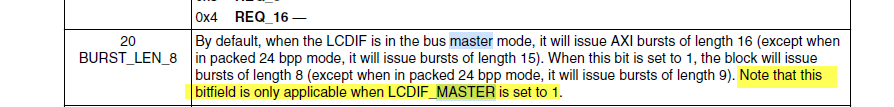

Also according to the App note: "Configure the eLCDIF AXI master feature register to improve the performance for 1280 × 800 LCD in the sd_jpeg.c. # In the bottom of function “void APP_ELCDIF_Init(void)”, add the line: APP_ELCDIF->CTRL2 = 0x00700000;"

I added the above line of code at the end of my void APP_ELCDIF_Init(void) function, and it just made my code stop running. Any comments on this suggestion?

Cheers!

Hi Andre marcus,

If you already prepare the frame buffer, I think you can use the memcpy,You totally can try it on your side.

About your APP_ELCDIF->CTRL2 = 0x00700000; stop running problem.

Do you set MASTER bit to 1?

You can check it on your side.

Wish it helps you!

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hello Kerry!!

i managed to solve y issue by disabling CachI and CachD; however, I was not able to meet the target of 60 frames per seconds using the function: App_fill_framebuffer, which uses a nested for loop. Could you please suggest how this code can be optimized for speed. Remember I’m using 1280x800.

Thanks

Hi Andre marcus,

Thanks for your updated information.

If you can't meet the target of 60 frames per seconds, it is still related to the HSW, HBP, HFP, VSW, VBP, VFP data of your LCD, I find you are totally use the application note data, but you didn't refer to your own LCD datasheet data.

In fact, I can't find the HSW, HBP, HFP, VSW, VBP, VFP data in the LCD file which you have shared.

Still as my reply in the previous time:

You need to find your own LCD controller related data, then define it in the code, and calculate the related video PLL output clock, and configure it in your project.

Wish it helps you!

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Andre marcus,

You heap and stack size is not the same as the application note, please modify the size like the AN, stack size is 0X8000, heap size is 0x800000.

Others, I still need more time to check details, will reply in the next week, because now I already out of work.

Thanks a lot for your understanding.

Best Regards,

Kerry

Hi Kerry!

I hope you can help me on this issue. Now my rgb code is running from the SDRAM. As I mentioned in my previous discussion, I modified evkmimxrt1060_elcdif_rgb so that it can run on a 1280x800 LCD. I sent you the data sheet in my previous posts. Now my issue is that I am seeing these signals: HSYNC, VSYNC, LCD_EN, and LCD_CLK (which I configured to be 70.5MHz). But I am not seeing any data on the data lines( R[0..7], G[0..7],B[0..7]). These signals are all pulled low when I check them with a scope. However, in a different test when I configured these data lines as GPIOs, I was able to toggle them. I don' t know if there is any register I need to access to enable data lines, if so please tell me. In the meantime, I attached below a copy of my code, please have a look and let me know if I am missing any configuration. I am just suspecting the SRDAM boot up to be the issue but I am not sure, as I am able to see the clocking signals. I also verified and I found that I am getting frame buffer fall at 60 Hz frequency.

Please help!

Attached project:

More investigation of the problem leads me to suspect that my main issue is the graphics data that I stored in the Cachable SDRAM memory space. I have 8MB of data per frame and that cannot be stored in the 2MB of non-cachable SDRAM memory space. As I declared my frame buffer as a global variable, it just got initialized to zero and that's why I am seeing a black screen all the time.

If I need to prevent this frame buffer data from being cached what should I do? the example I was looking at was dealing with a 2MB of data which got stored as non-cachable and that was it.

I hope someone can comment as soon as possible.

Cheers!

Hi Andre marcus,

You can disable the cache, then test it directly.

Comment :

SCB_EnableDCache();

SCB_EnableICache();

In BOARD_ConfigMPU();

Then you don't need to care about your non-cachable memory is not enough, just test it to check whether your problem is related to the cache.

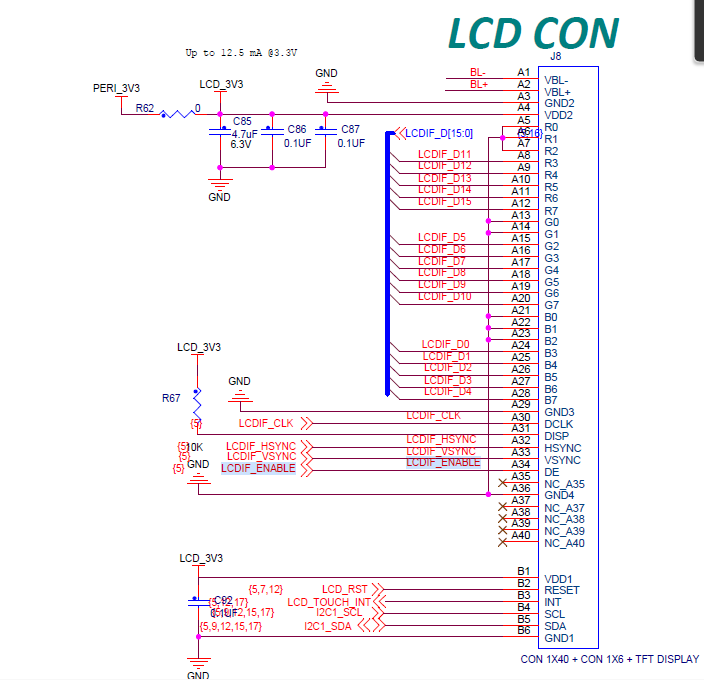

BTW, please share me your hardware schematic, I really need to know how you connect LCD to the RT chip.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Andre marcus,

Could you please give me your RT schematic picture which used to connect your LCD pins?

I just need to check it, because I need to know which RGB signal you have connected, if your schematic is important, you don't need to send me the whole file, you just need to give me some picture about it, just like this:

Then I can help you more details.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------