- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Hi All

In an environment with HS USB host and Ethernet on the i.MX RT 1062 we are finding that there are some Ethernet CRC errors being detected and it looks to happen when the HS USB is performing transfers at the same time.

Since the Ethernet reception is controlled by HW (dedicated DMA to RAM) it is expected that the issue is that the HS USB's bus master is not allowing the Ethernet bus master adequate resources for it to ensure that it can save the received data - the result being that Ethernet Rx bytes are lost, resulting in CRC32 errors on the Ethernet bus.

What possibilities does the processor have to control the bus master's priorities or load balancing that may be used to avoid such issues?

Thanks!

Regards

Mark

已解决! 转到解答。

Hello @mjbcswitzerland,

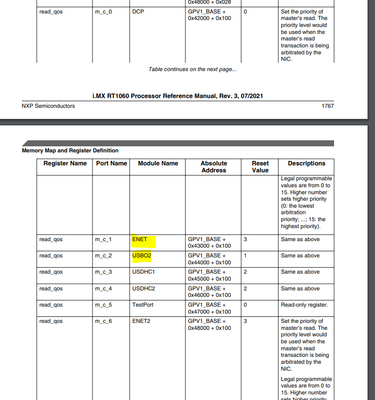

I think you should consult Chapter 29: Network Interconnect Bus System

it is a configurable AXI arbiter between several masters and slaves

That will help you increase priority as you need.

Please check following specifically:

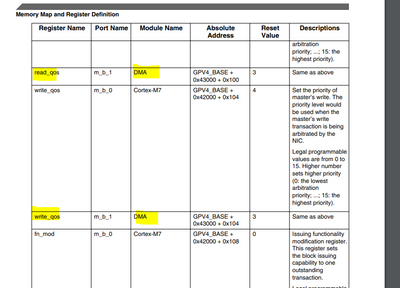

You might also need to increase priority of DMA

@mjbcswitzerland you said you opened a support case. Please close this one by marking it helpful/solved.

And we will continue support in the case (as you might reveal more details about your specific architecture)

Thank you in advance,

Best regards

Seif

Hello @mjbcswitzerland,

I think you should consult Chapter 29: Network Interconnect Bus System

it is a configurable AXI arbiter between several masters and slaves

That will help you increase priority as you need.

Please check following specifically:

You might also need to increase priority of DMA

@mjbcswitzerland you said you opened a support case. Please close this one by marking it helpful/solved.

And we will continue support in the case (as you might reveal more details about your specific architecture)

Thank you in advance,

Best regards

Seif

Hi

Many thanks for pointing out the NIC-301.

I have downloaded the ARM document "CoreLink™ Network Interconnect NIC-301 Revision: r2p3"

Looking at the bus master priorities I see that Ethernet is set up in the device to have a priority of 3 and the HSUSB to have a priority of 2, which I also verified by reading the core's registers, which would suggest that HS USB will not cause the Ethernet receptions to be blocked by its own operation.

I'll do some further testing though and contact you in the support case should the situation not be improved by this work.

Thanks

Regards

Mark