- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- RT1064 / Enable all 1MB SRAM for Zephyr [Resize OCRAM]

RT1064 / Enable all 1MB SRAM for Zephyr [Resize OCRAM]

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

RT1064 / Enable all 1MB SRAM for Zephyr [Resize OCRAM]

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

By default the Zephyr devicetree for MIMXRT1064-EVK gives access to only 768KB of SRAM (OCRAM). My application needs access to the full 1MB of SRAM available on-chip. I would like to disable ITCM/DTCM and have one contiguous OCRAM memory block from 0x20200000 to 0x202fffff.

The device tree has been modiffied with the following overlay:

/ {

soc {

flexram: flexram@400b0000 {

itcm: itcm@0 {

status = "disabled";

};

dtcm: dtcm@20000000 {

status = "disabled";

};

ocram: ocram@20200000 {

status = "okay";

reg = < 0x20200000 0x100000 >;

};

};

};

};

/ {

chosen {

zephyr,sram = &ocram;

};

};

Result of compilation (1MB of SRAM seemingly available):

[100%] Linking C executable zephyr.elf

Memory region Used Size Region Size %age Used

SDRAM: 0 GB 32 MB 0.00%

FLASH: 912064 B 4 MB 21.75%

SRAM: 418773 B 1 MB 39.94%

IDT_LIST: 0 GB 2 KB 0.00%

Generating files from zephyr.elf for board: mimxrt1064_evk

[100%] Built target zephyr_final

This device tree change does not automatically change the ITCM/DTCM/OCRAM memory allocations. To do so I have added the following code to Reset.S:

/* Configure RT1064 for 1MB OCRAM */

cpsid i // Mask interrupts|

LDR R0, =0x400ac044 // IOMUXC_GPR_GPR17

LDR R1, =0x55555555 //

STR R1, [R0] // [IOMUXC_GPR_GPR17] := 0x55555555 (All banks OCRAM)

LDR R0, =0x400ac040 // IOMUXC_GPR_GPR16

LDR R1, =0x04 //

LDR R3, [R0] // R3 := [IOMUXC_GPR_GPR16]

BFC R3, #0,#2 // Clear bits D1 & D0 of R3 to disable DTCM and ITCM

ORR R2, R1,R3 // R2 := R3 OR R1 (0x04 == use FLEXRAM_BANK_CFG to config)

STR R2, [R0] // [IOMUXC_GPR_GPR16] := (use FLEXRAM_BANK_CFG to config)

LDR R0, =0x400ac038 // IOMUXC_GPR_GPR14

LDR R1, [R0] // R1 := [IOMUXC_GPR_GPR14]

BFC R1, #16,#8 // Clear bits D23-D16 of R1 to set DTCM and ITCM sizes to 0

STR R1, [R0] // [IOMUXC_GPR_GPR14] := Size of DTCM/ITCM adjusted down to 0

cpsie i // Unmask interrupts

A peek at the zephyr.lst file shows that the reset vector indeed points to __start,

70002000 <_vector_table>:

70002000: 88 78 25 20 0d 14 07 70 71 06 0a 70 79 14 07 70 .x% ...pq..py..p

70002010: 79 14 07 70 79 14 07 70 79 14 07 70 00 00 00 00 y..py..py..p....

where my inserted code is the first to run:

7007140c <__start>:

SECTION_SUBSEC_FUNC(TEXT,_reset_section,__start)

/* Configure RT1064 for 1MB OCRAM */

cpsid i // Mask interrupts|

7007140c: b672 cpsid i

LDR R0, =0x400ac044 // IOMUXC_GPR_GPR17

7007140e: 4816 ldr r0, [pc, #88] ; (70071468 <__start+0x5c>)

LDR R1, =0x55555555 //

70071410: f04f 3155 mov.w r1, #1431655765 ; 0x55555555

STR R1, [R0] // [IOMUXC_GPR_GPR17] := 0x55555555 (All banks OCRAM)

70071414: 6001 str r1, [r0, #0]

LDR R0, =0x400ac040 // IOMUXC_GPR_GPR16

70071416: 4815 ldr r0, [pc, #84] ; (7007146c <__start+0x60>)

LDR R1, =0x04 //

70071418: f04f 0104 mov.w r1, #4

LDR R3, [R0] // R3 := [IOMUXC_GPR_GPR16]

7007141c: 6803 ldr r3, [r0, #0]

BFC R3, #0,#2 // Clear bits D1 & D0 of R3 to disable DTCM and ITCM

7007141e: f36f 0301 bfc r3, #0, #2

ORR R2, R1,R3 // R2 := R3 OR R1 (0x04 == use FLEXRAM_BANK_CFG to config)

70071422: ea41 0203 orr.w r2, r1, r3

STR R2, [R0] // [IOMUXC_GPR_GPR16] := (use FLEXRAM_BANK_CFG to config)

70071426: 6002 str r2, [r0, #0]

LDR R0, =0x400ac038 // IOMUXC_GPR_GPR14

70071428: 4811 ldr r0, [pc, #68] ; (70071470 <__start+0x64>)

LDR R1, [R0] // R1 := [IOMUXC_GPR_GPR14]

7007142a: 6801 ldr r1, [r0, #0]

BFC R1, #16,#8 // Clear bits D23-D16 of R1 to set DTCM and ITCM sizes to 0

7007142c: f36f 4117 bfc r1, #16, #8

STR R1, [R0] // [IOMUXC_GPR_GPR14] := Size of DTCM/ITCM adjusted down to 0

70071430: 6001 str r1, [r0, #0]

cpsie i // Unmask interrupts

70071432: b662 cpsie i

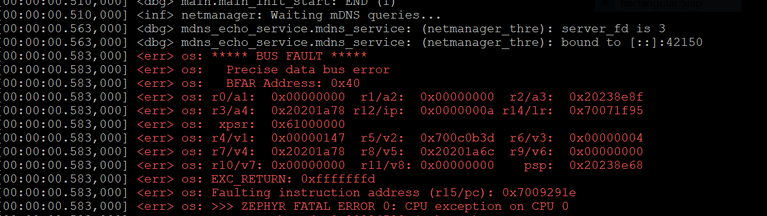

When run a lot of the initial expected log is shown in console but eventually the system crashes before the boot process completes:

If I keep the OCRAM at the default 768KB and make no changes to Reset.S then the system boots nicely w/o any problems.

Very grateful for any pointers as to what I am doing wrong here.

/Rolf