- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- Re: RT1052CVL5B uses FLEXPWM and eDMA output and capture PWM

RT1052CVL5B uses FLEXPWM and eDMA output and capture PWM

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

RT1052CVL5B uses FLEXPWM and eDMA output and capture PWM

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello

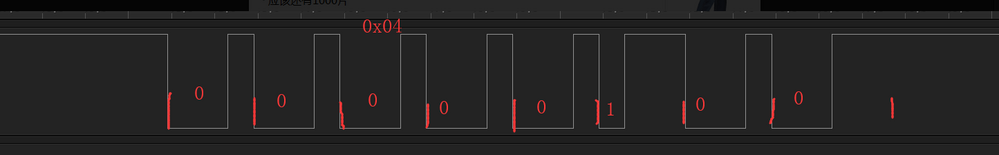

我使用 PWM1模块3的PwmA通道 在 STS[RF](Reload Flag) 置位时 触发 eDMA0通道8 写 VALX寄存器。 通过DMA0传输,使PWM1模块3的PwmA通道输出8个占空比不同、周期相同的波形,用来表示一个字节的数据,如下图表示0x04,发送的8个周期分别代表位 0000 0100。

随后使用 PWM2模块3的PwmA通道 捕获 上面输出的波形 来触发 DMA0通道4 读捕获寄存器。DMA0通道4 用来传输 CVAL2寄存器 的值到定义的数组; DMA0通道4 链接 通道5 来传输CVAL2CYC的值; 通道5 链接 通道6 来传输CVAL3的值;通道6 链接 通道7 来传输CVAL3CYC的值。PWM2模块3的PwmA通道 设置为 A0 下降沿捕获, A1 上升沿捕获, A0捕获 && A1捕获 触发DMA传输。

调试时,发现了几个问题:

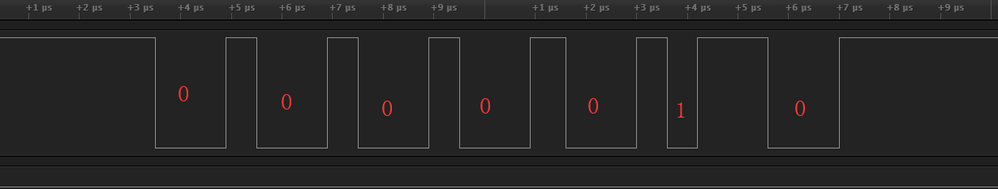

1. PWM1 产生波形时,有可能会丢掉第一个周期,如图:这理论上是发送 0x02(0000 0010),实际发送的却少了一个周期(000 0010)

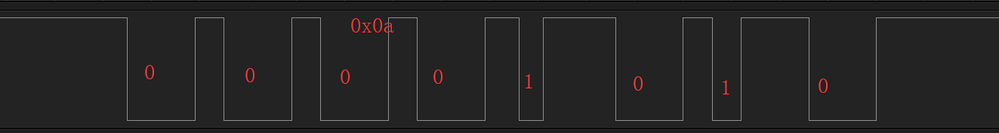

2. 在PWM1发送的波形无误的情况下,PWM2捕获波形后通过DMA传输到内存的数据可能会漏掉第一个周期。如下: 图是PWM1发送的波形0x0a(00001010),是正确的;g_CVALx和g_CVALxCYC是PWM2捕获下图中波形,通过DMA传输到内存的捕获寄存器数据。出错的寄存机值见 g_CVAL2[7];g_CVAL2[7] 理论值是要比g_CVAL2[6] (26288)大,实际g_CVAL2[7]的值是初始化值7(数组初始化时赋的初始值)。

g_CVAL2[0] = 24181

g_CVAL2CYC[0] = 4

g_CVAL3[0] = 24392

g_CVAL3CYC[0] = 4

g_CVAL2[1] = 24482

g_CVAL2CYC[1] = 4

g_CVAL3[1] = 24692

g_CVAL3CYC[1] = 4

g_CVAL2[2] = 24783

g_CVAL2CYC[2] = 4

g_CVAL3[2] = 24994

g_CVAL3CYC[2] = 4

g_CVAL2[3] = 25084

g_CVAL2CYC[3] = 4

g_CVAL3[3] = 25294

g_CVAL3CYC[3] = 4

g_CVAL2[4] = 25385

g_CVAL2CYC[4] = 4

g_CVAL3[4] = 25294 //在这里,本来DMA传输过来的应该是比 g_CVAL2[4] 大的值,结果传输的是 上一次捕获的

g_CVAL3CYC[4] = 4 //g_CVAL3[3] 的值

g_CVAL2[5] = 25987

g_CVAL2CYC[5] = 4

g_CVAL3[5] = 25896

g_CVAL3CYC[5] = 4

g_CVAL2[6] = 26288

g_CVAL2CYC[6] = 4

g_CVAL3[6] = 26499

g_CVAL3CYC[6] = 4

g_CVAL2[7] = 7

g_CVAL2CYC[7] = 70 //7 和 70 是初始值,本来应该是和前面一样有正确数据的,

g_CVAL3[7] = 7 //这部分,DMA没传输数据过来

g_CVAL3CYC[7] = 70

3. 在PWM1发送的波形无误的情况下,DMA传输到内存的数据可能是上次捕获的捕获寄存器值。如上: 见 g_CVAL3[4] 和 g_CVAL3[3];g_CVAL3[4] 理论值是要比 g_CVAL3[3] (25294)大,实际g_CVAL3[4]的值等于g_CVAL3[3] 的值。

4. 在计数器从65535->0时,如果在等于0时捕获成功,则可能出现这种情况,CVAL2 捕获值为0,但CVAL2CYC捕获的值没加1.如下:g_CVAL2CYC[3] = 1,理论上应该 g_CVAL2CYC[3] = 2

g_CVAL2[1] = 64934

g_CVAL2CYC[1] = 1

g_CVAL3[1] = 65144

g_CVAL3CYC[1] = 1

g_CVAL2[2] = 65235

g_CVAL2CYC[2] = 1

g_CVAL3[2] = 65446

g_CVAL3CYC[2] = 1

g_CVAL2[3] = 0

g_CVAL2CYC[3] = 1 //这里理论值应该是2,实际捕获到的是1

g_CVAL3[3] = 210

g_CVAL3CYC[3] = 2

g_CVAL2[4] = 300

g_CVAL2CYC[4] = 2

g_CVAL3[4] = 391

g_CVAL3CYC[4] = 2

5. 以上第1、2、3、点,在输出波形的频率越低时出现的概率越小,在10K时,基本上不会出现这些错误,在500k时,这些错误出现的概率就比较多了。

我估计应该是PWM的配置问题,是我哪里没有配置好吗?需要注意哪些方面?

我将我测试的代码放进附录。

Best regards,

Torstei

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

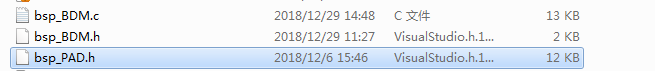

purongyu,could you provide the "bsp_bdm.h" file? I cannot find it in your attachment.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello

My phone number: +86 13058085495

Background of the project: This is a programmer project, this is a chip programming protocol.

The only statement in the file "bsp_bdm.h" is the test function (void BDM( void );).

Thank you for your help!

Best regards,

Aldo.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Purong,

Per our talk, you had implemented the your target fucntion by Qtimer and eDMA. Could you provide the codes of Qtimer and eDMA? Then I can compare them with that of FLEXPWM and eDMA to try to figure out the problem. Thanks!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

which SDK are you using?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello

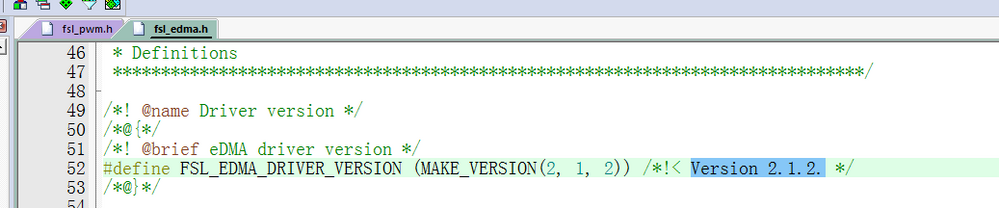

The version in "fsl_edma.h" is "Version 2.1.2", as shown below:

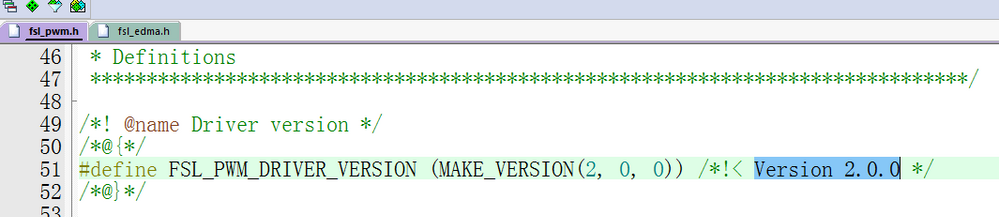

The version in "fsl_pwm.h" is "Version 2.0.0", as shown below:

After verification, the library versions of these two modules are up to date.

Best regards,

Aldo.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello purongyu

could you please provide your contact information? I want to know some background about this project. Thanks!