- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- IMXRT117x PCB design: is it recommended to short the DCDC_DIG and VDD_SOC_IN by same plane?

IMXRT117x PCB design: is it recommended to short the DCDC_DIG and VDD_SOC_IN by same plane?

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I'm designing a custom board based on IMXRT1175DVMAA, and plan to use the internal DCDC to output supply the MCU core power 'VDD_SOC_IN'. I noticed the EVK design used some jump resistors between DCDC output 'DCDC_DIG' and core power 'VDD_SOC_IN', my question is: can I remove these resistors in my design? then the power plane of 'DCDC_DIG' and 'VDD_SOC_IN' will be connected directly, whether it will introduce noise form DCDC to MCU core power directly?

Or, is it recommended a resistor/ferrite bead to separate the power plane of 'DCDC_DIG' and 'VDD_SOC_IN', for EMC consideration?

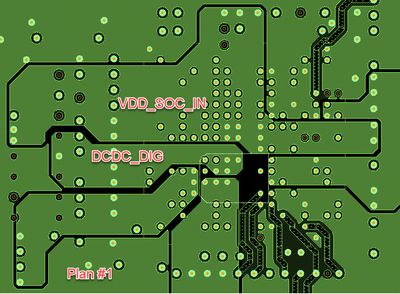

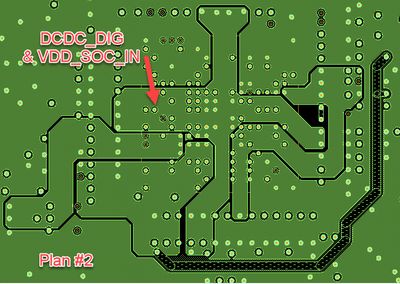

In my design, I have to place all the decoupling/buck capacitors around MCU chip on same PCB side, due to the mechanical limitation. So the actual PCB layout will be as follows, please comment which on will be better, thanks!

Plan #1 Separate the DCDC_DIG and VDD_SOC_IN

Plan #1 Separate the DCDC_DIG and VDD_SOC_IN Plan #2 Shorting the DCDC_DIG and VDD_SOC_IN

Plan #2 Shorting the DCDC_DIG and VDD_SOC_INBR

Tyrone Liu

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Additionally, this application note might be helpful to improve the EMC performance: EMC Design Recommendation on i.MXRT Series (nxp.com)

This application note along with the Hardware Development Guide have the guidelines for a good design.

Bes regards,

Omar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello

I Hope you are well.

They can be tied together, but we need to assure that DCDC current loop is small as possible. The #2 option is correct but from my perspective the trace is long, please correct me if I'm wrong.

To keep good EMC performance, the below items are critical for the layout of DCDC circuit.

• Keep the DC/DC current loop as small as possible to avoid EMI issues.

• Enable current first pass through filter capacitors and then go to pins.

• Avoid unnecessary via between inductor and bulk capacitors.

If you have more questions do not hesitate to ask me.

Best regards,

Omar

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Omar,

Thanks for your comment, I think this general requirement is correspond to our EMC concern, thus I decide to adopt #1 option.

- Enable current first pass through filter capacitors and then go to pins.

Best Regard

Tyrone

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Additionally, this application note might be helpful to improve the EMC performance: EMC Design Recommendation on i.MXRT Series (nxp.com)

This application note along with the Hardware Development Guide have the guidelines for a good design.

Bes regards,

Omar