- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- Re: Bug in "fsl_flexcan.c" / wrong treatment of the 'FDRATE'-bit

Bug in "fsl_flexcan.c" / wrong treatment of the 'FDRATE'-bit

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Greetings all,

Just about to get my feet wet with CAN FD in an RT1064, and had a first look at what was provided by NXP.

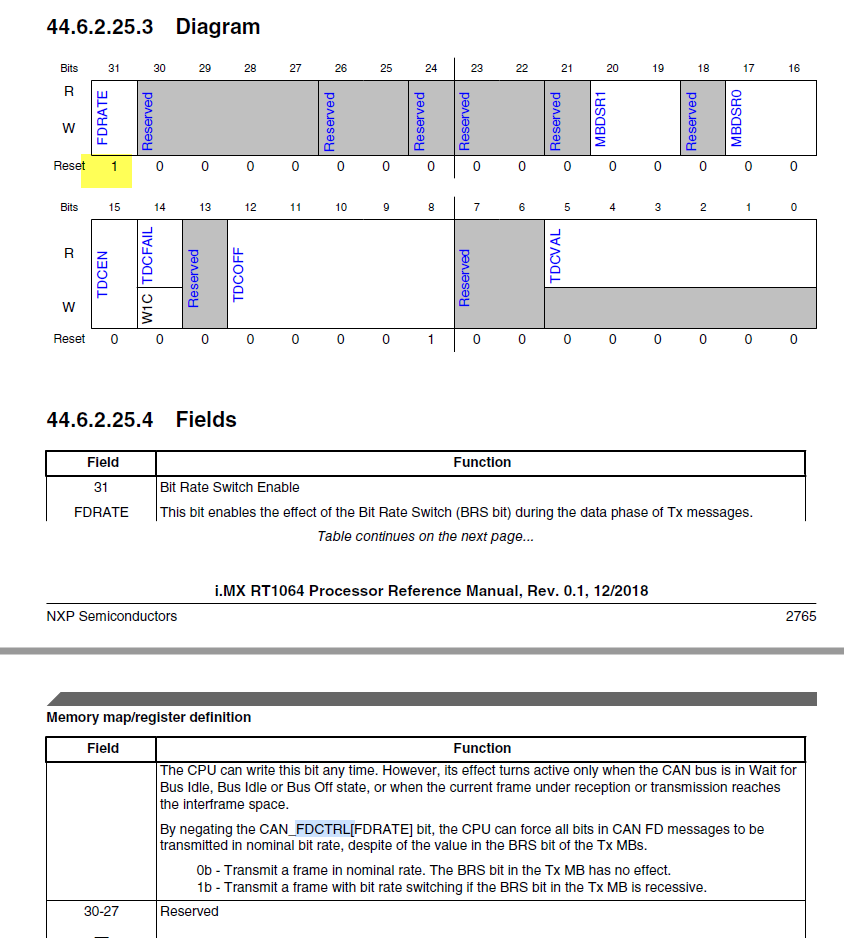

I think there's a bug in the treatment of the 'FDRATE'-bit (31) in register 'FDCTRL', module "fsl_flexcan.c" (at least with the one used by the "canfd_interrupt_transfer" demo provided for the RT1064 evaluation board). It's in this function:

void FLEXCAN_FDInit( CAN_Type *base, const flexcan_config_t *config, uint32_t sourceClock_Hz, flexcan_mb_size_t dataSize, bool brs)

Here, "bool brs" means "bitrate switch enable" (TRUE=allow transmission and reception of CAN FD messages, FALSE=only allow normal "CAN" frames regardless of the mailbox/message-buffer configuration). I guess this should be mapped to register 'FDCTRL', bit 'FDRATE' ("brs" = "FDRATE", oh well...) .

Here is what I think is wrong - C++ style comments were added by myself, when trying to understand what this code was supposed to do:

/* Enable FD operation and set bitrate switch. */

if (brs)

{

base->FDCTRL &= CAN_FDCTRL_FDRATE_MASK; // CLEAR anything except 'FDRATE' (bit 31) ? ? ?

}

else // disable "FD"-operation (allow "normal" CAN frames only)

{

base->FDCTRL &= ~CAN_FDCTRL_FDRATE_MASK; // CLEAR the 'FDRATE'-bit (31)

}

What *I guess* should be done in FLEXCAN_FDInit() is :

/* Enable FD operation and set bitrate switch. */

if (brs)

{

base->FDCTRL |= CAN_FDCTRL_FDRATE_MASK; // SET 'FDRATE' but leave other bits unchanged

}

else // disable "FD"-operation (allow "normal" CAN frames only)

{

base->FDCTRL &= ~CAN_FDCTRL_FDRATE_MASK; // CLEAR the 'FDRATE'-bit (31)

}

Strangely, even with the original code (which either clears ANYTHING BUT 'FDRATE' or clears only 'FDRATE', but never sets that bit), I am able to transmit "FD"-frames besides normal CAN frames.

Maybe NXP can correct this, or (if the strange bitwise-and to clear ANYTHING BUT 'FDRATE' was intended this way), add a helpful hint / comment in the sourcecode, documenting why the bit isn't bitwise OR-ed to "set" it in Mr. FlexCAN(3).

Cheers, Wolfgang .

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Wolfgang Buescher ,

Thanks a lot for your bug report.

I totally agree with you that the code is wrong, it should be:

/* Enable FD operation and set bitrate switch. */

if (brs)

{

base->FDCTRL |= CAN_FDCTRL_FDRATE_MASK; // SET 'FDRATE' but leave other bits unchanged

}

You can make it works, because the FDRATE bit is 1 after reset.

I will report this bug to our related department, and it will be fixed in the next SDK version.

Thanks again for the valuable contribution.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Wolfgang Buescher ,

Thanks a lot for your bug report.

I totally agree with you that the code is wrong, it should be:

/* Enable FD operation and set bitrate switch. */

if (brs)

{

base->FDCTRL |= CAN_FDCTRL_FDRATE_MASK; // SET 'FDRATE' but leave other bits unchanged

}

You can make it works, because the FDRATE bit is 1 after reset.

I will report this bug to our related department, and it will be fixed in the next SDK version.

Thanks again for the valuable contribution.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Kerry. The reset-value "set" = FDRATE enabled perfectly explains why the code works, as long as you never turned 'FDRATE' off in your application (and that's what happened here, and caused a bit of head-scratching).

The next issue (in another thread, #503656) about not being able to access certain 'Enhanced' timing registers seems a tougher nut to crack. But that's OT here. Case closed.

Have a nice day,

Wolf .