- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: uboot logo color is not normal

uboot logo color is not normal

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Community,

board: imx6q;

version: u-boot-2009.08;

i did what this doc said: https://community.nxp.com/docs/DOC-98109

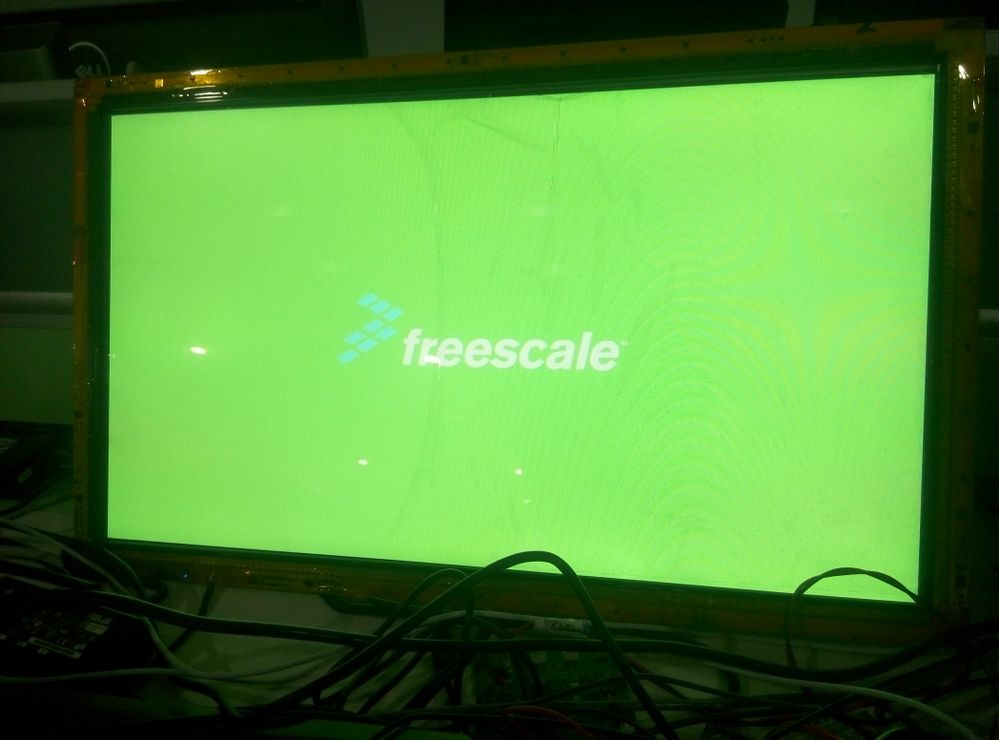

but the logo color is not normal, it si green like this:

what is wrong? and this is my head file:

//#define IPU_OUTPUT_MODE_HDMI

#define IPU_OUTPUT_MODE_LVDS

// #define IPU_OUTPUT_MODE_LCD

#ifdef IPU_OUTPUT_MODE_LVDS

// For LVDS, 1920*1080 resolution, dual channel

#define DISPLAY_WIDTH 1920

#define DISPLAY_HEIGHT 1080

#define DISPLAY_BPP 32

#define DISPLAY_IF_BPP 24 // RGB24 interface

#define DISPLAY_HSYNC_START 80

#define DISPLAY_HSYNC_END 68

#define DISPLAY_HSYNC_WIDTH 12

#define DISPLAY_VSYNC_START 15

#define DISPLAY_VSYNC_END 15

#define DISPLAY_VSYNC_WIDTH 8

#define DISPLAY_PIX_CLOCK 139526400 //(DISPLAY_HSYNC_START + DISPLAY_HSYNC_END + DISPLAY_HSYNC_WIDTH + DISPLAY_WIDTH) *

(DISPLAY_VSYNC_START + DISPLAY_VSYNC_END + DISPLAY_VSYNC_WIDTH + DISPLAY_HEIGHT) * refresh rate (60Hz)

#define LVDS_SPLIT_MODE // For dual channel split mode.

#define DISPLAY_VSYNC_POLARITY 1

#define DISPLAY_HSYNC_POLARITY 1

#define DISPLAY_CLOCK_POLARITY 1

#define DISPLAY_DATA_POLARITY 0

#define DISPLAY_DATA_ENABLE_POLARITY 1

#define IPU_NUM 1 // 1 for IPU1, 2 for IPU2.

#define DI_NUM 0 // 0 for DI0, 1 for DI1.

#define LVDS_PORT 0 // 0 for LVDS0, 1 for LVDS1.

#define DI_CLOCK_EXTERNAL_MODE //When clock external mode was defined, the DI clock root will be PLL3 PFD1,

//without this macro, the DI root clock is IPU internal clock.

nothing changed, just above, can you help me? what should i do? what is info do you need? tell me.

wating for your reply?

thank you.

fulinux.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I had identified the issue, please apply the attached uboot patch to fix it.

it is based on JB4.3_1.1.1_uboot_logo_keep_patch_2015-09-18.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

kernel logo can show ppm file not bmp file, it is not logo file's problem, when i write 0x00 to fb memory is also little white. i have told you above. it is very strange.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In linux, you can use dd command to show the bmp file to frame buffer:

dd if=logo.bmp of=/dev/fb0 bs=1 skip=54

You'd better find out the different display setting in your kernel and uboot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Qiang,

I have the same problem. It may have some problem with the 0001-Enable-uboot-logo-for-HDMI-LCD-and-LVDS.patch. The LVDS CLK is about 75M no matter what the DISPLAY_PIX_CLOCK is. Woud you mind testing for what I said?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Qiang,

i did as you said, i shows well:

do you need any information? pls tell me.

thank you,

fulinux.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Maybe there is some wrong porting code in your uboot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, do you need my uboot code?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OK, i will test as you said;

and look at this:

pData = (unsigned char *)CONFIG_FB_BASE; CONFIG_FB_BASE = 0x27B00000

and i have write 0x00000 from 0x27B00000 to 0x27B00000 + bmp file size. and read memory by "md" command it shows right:

MX6Q SABRESD U-Boot > md 0x27B00000

27b00000: 00000000 00000000 00000000 00000000 ................

27b00010: 00000000 00000000 00000000 00000000 ................

27b00020: 00000000 00000000 00000000 00000000 ................

27b00030: 00000000 00000000 00000000 00000000 ................

....

but now, the lcd panel is still litte white:

but it is not more white than when i write 0xfffffff to fb memory. i don't know if you know what i mean.

thank you,

fulinux.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi Qiang,

is it wrong with my backlight and lcd power settings of gpios, this is my settings:

at setup_lvds_iomux() function in board/freescale/mx6q_sabresd/mx6q_sabresd.c:

#if defined CONFIG_MX6Q

/* GPIO backlight */

//mxc_iomux_v3_setup_pad(MX6Q_PAD_SD1_DAT3__PWM1_PWMO);

mxc_iomux_v3_setup_pad(MX6Q_PAD_GPIO_9__PWM1_PWMO);

/* LVDS panel CABC_EN */

mxc_iomux_v3_setup_pad(MX6Q_PAD_NANDF_CS2__GPIO_6_15);

mxc_iomux_v3_setup_pad(MX6Q_PAD_NANDF_CS3__GPIO_6_16);

mxc_iomux_v3_setup_pad(MX6Q_PAD_GPIO_2__GPIO_1_2);

mxc_iomux_v3_setup_pad(MX6Q_PAD_GPIO_7__GPIO_1_7);

mxc_iomux_v3_setup_pad(MX6Q_PAD_GPIO_19__GPIO_4_5);

reg = readl(GPIO6_BASE_ADDR + GPIO_DR);

reg &= ~(1 << 16);

writel(reg, GPIO6_BASE_ADDR + GPIO_DR);

#if 1

gpio_direction_output(IMX_GPIO_NR(1, 2), 1);

udelay(10 * 1000);

gpio_set_value(IMX_GPIO_NR(1, 2), 0);

udelay(10 * 1000);

gpio_set_value(IMX_GPIO_NR(1, 2), 1);

gpio_direction_output(IMX_GPIO_NR(4, 5), 1);

udelay(10 * 1000);

gpio_set_value(IMX_GPIO_NR(4, 5), 1);

gpio_direction_output(IMX_GPIO_NR(1, 7), 0);

udelay(10 * 1000);

gpio_set_value(IMX_GPIO_NR(1, 7), 0);

#endif

at board_late_init() function:

ipu_display_setup();

gpio_set_value(IMX_GPIO_NR(1, 7), 1);

udelay(10 * 1000);

gpio_set_value(IMX_GPIO_NR(4, 5), 0);

Do you think that was right?

with my attach file.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

when i modified this:

#define DISPLAY_WIDTH 1920

#define DISPLAY_HEIGHT 1080

#define DISPLAY_BPP 32

#define DISPLAY_IF_BPP 24 // RGB24 interface

#define DISPLAY_HSYNC_START 80

#define DISPLAY_HSYNC_END 68

#define DISPLAY_HSYNC_WIDTH 12

#define DISPLAY_VSYNC_START 15

#define DISPLAY_VSYNC_END 15

#define DISPLAY_VSYNC_WIDTH 8

#define DISPLAY_PIX_CLOCK 139526400 //(DISPLAY_HSYNC_START + DISPLAY_HSYNC_END + DISPLAY_HSYNC_WIDTH + DISPLAY_WIDTH) *

(DISPLAY_VSYNC_START + DISPLAY_VSYNC_END + DISPLAY_VSYNC_WIDTH + DISPLAY_HEIGHT) * refresh rate (60Hz)

#define LVDS_SPLIT_MODE 1 // For dual channel split mode.

#endif

#define DISPLAY_VSYNC_POLARITY 0

#define DISPLAY_HSYNC_POLARITY 0

#define DISPLAY_CLOCK_POLARITY 1

#define DISPLAY_DATA_POLARITY 0

#define DISPLAY_DATA_ENABLE_POLARITY 1

#define IPU_NUM 1 // 1 for IPU1, 2 for IPU2.

#define DI_NUM 0 // 0 for DI0, 1 for DI1.

#define LVDS_PORT 1 // 0 for LVDS0, 1 for LVDS1.

#define DI_CLOCK_EXTERNAL_MODE //When clock external mode was defined, the DI clock root will be PLL3 PFD1,

//without this macro, the DI root clock is IPU internal clock.

and

bmpReady = 0;

if (bmpReady == 0) {

// Fill RGB frame buffer

// Red

for (i = 0; i < (DISPLAY_WIDTH * DISPLAY_HEIGHT * (DISPLAY_BPP / 8) / 3); i += (DISPLAY_BPP / 8)) {

#if (DISPLAY_BPP == 16)

pData[i + 0] = 0x00;

pData[i + 1] = 0xF8;

#else

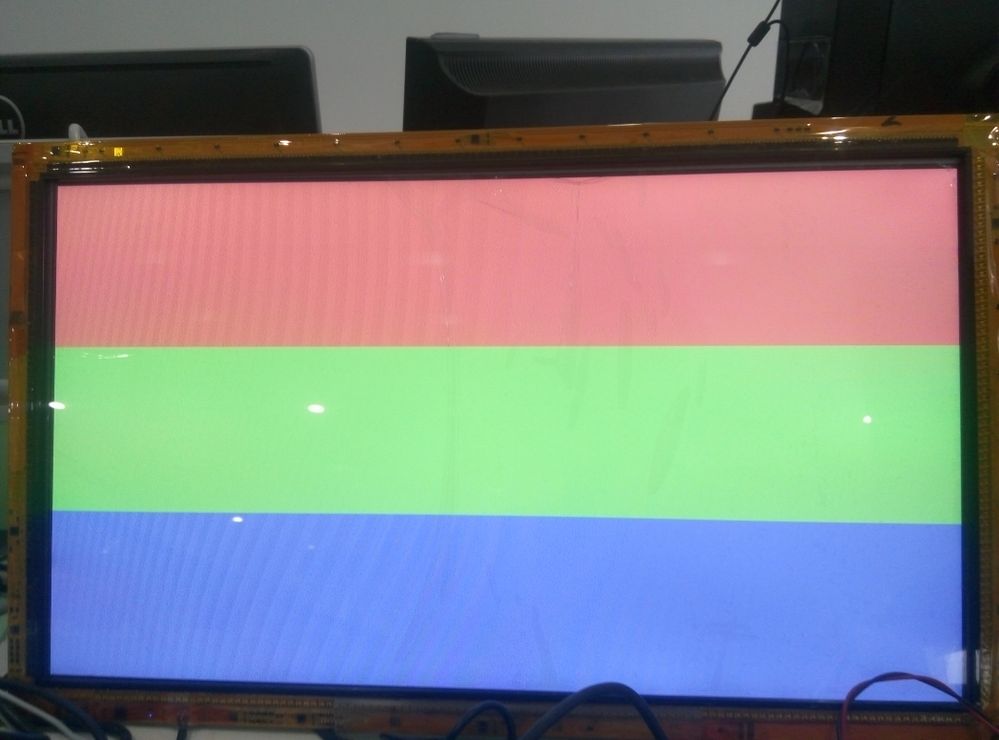

and the lcd panel screen display like this:

you can look at this, the color is lighter;

when i change code like this, change "pData[] = 0x FF" to 0x00:

// Red

for (i = 0; i < (DISPLAY_WIDTH * DISPLAY_HEIGHT * (DISPLAY_BPP / 8) / 3); i += (DISPLAY_BPP / 8)) {

#if (DISPLAY_BPP == 16)

pData[i + 0] = 0x00;

pData[i + 1] = 0xF8;

#else

pData[i + 0] = 0x00;

pData[i + 1] = 0x00;

pData[i + 2] = 0x00;

pData[i + 3] = 0x00;

#endif

}

// Green

for (; i < (DISPLAY_WIDTH * DISPLAY_HEIGHT * (DISPLAY_BPP / 8) / 3) * 2; i += (DISPLAY_BPP / 8)) {

#if (DISPLAY_BPP == 16)

pData[i + 0] = 0xE0;

pData[i + 1] = 0x07;

#else

pData[i + 0] = 0x00;

pData[i + 1] = 0x00;

pData[i + 2] = 0x00;

pData[i + 3] = 0x00;

#endif

}

// Blue

for (; i < DISPLAY_WIDTH * DISPLAY_HEIGHT * (DISPLAY_BPP / 8); i += (DISPLAY_BPP / 8)) {

#if (DISPLAY_BPP == 16)

pData[i + 0] = 0x1F;

pData[i + 1] = 0x00;

#else

pData[i + 0] = 0x00;

pData[i + 1] = 0x00;

pData[i + 2] = 0x00;

pData[i + 3] = 0x00;

then like this:

it should be black,but it is whilt!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi,

could you tell me the path of file where you insert bmpReady = 0;

thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, from your kernel setting, the DE is high active, so it should be "#define DISPLAY_DATA_ENABLE_POLARITY 1"

For black to white issue, you can change DISPLAY_DATA_POLARITY from 0 to 1 to invert the data line.

I think all these informations should be found from your panel's datasheet.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

when it should be black it shows white, but when it should be whilt it shows more white, so it can't shows black.

when i change "#define IPU_NUM 1" to 2,it shows white, red and blue looply, why

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Another thing can be tried: invert the clock polarity, change DISPLAY_CLOCK_POLARITY from 1 to 0.

The display shows white, red and blue looply, that means the panel hasn't found valid input signal and show its test pattern.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

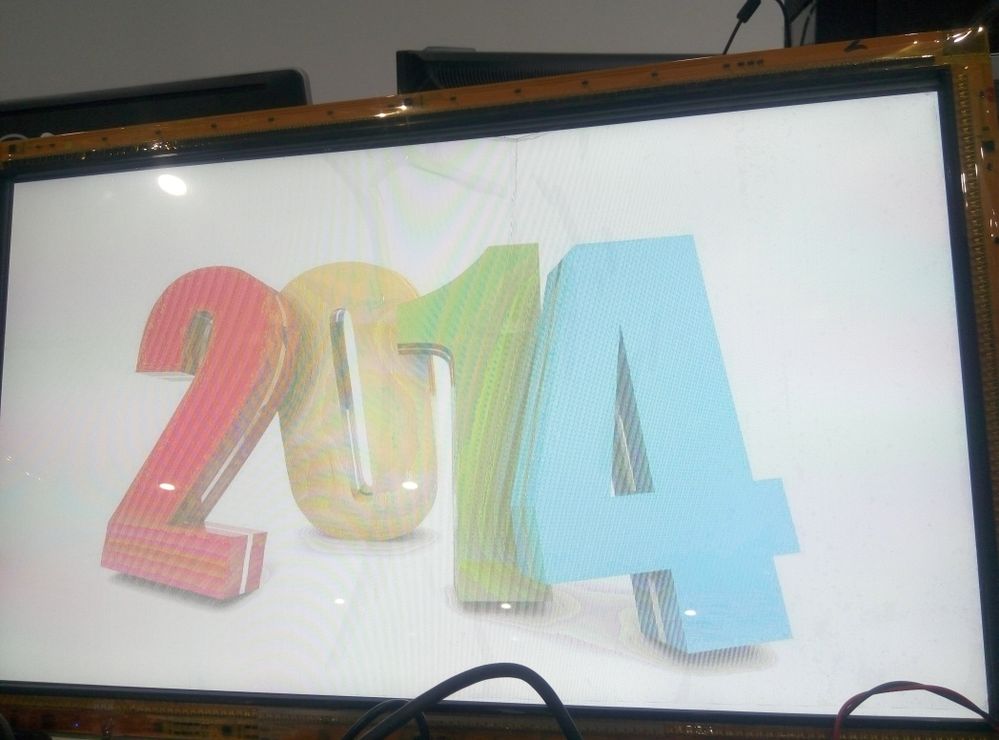

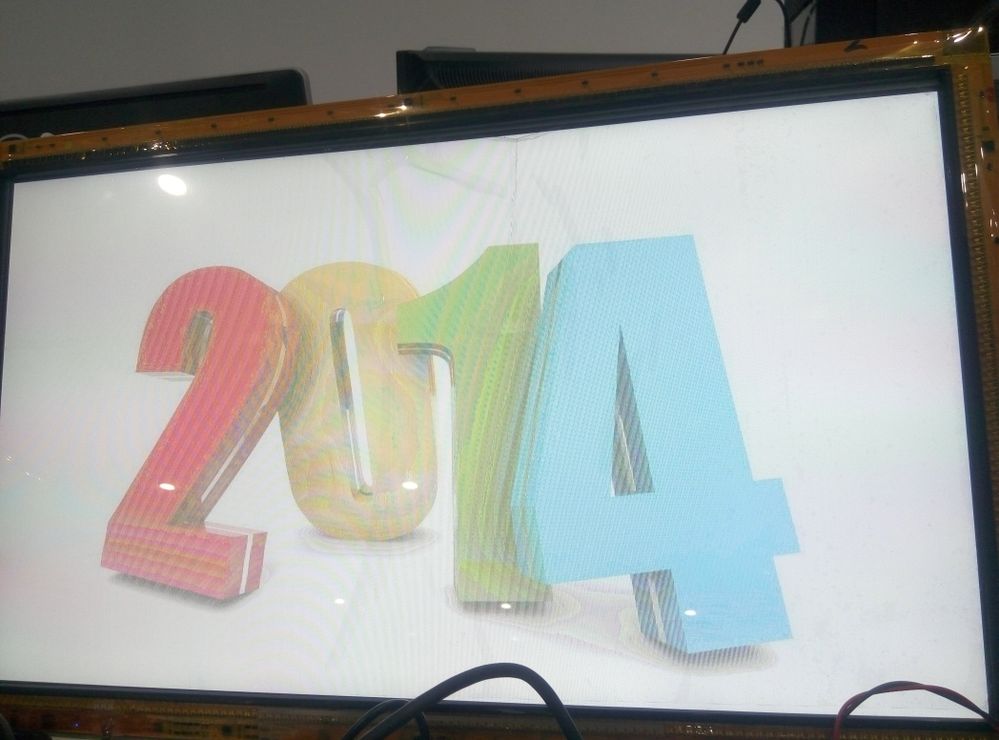

it dosen't change anything when i change DISPLAY_CLOCK_POLARITY from 1 to 0. this is logo picture(original picture):

this is the screen shows:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you attach your bmp file and panel datasheet here?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From the datasheet, the setting should be followed, no other issues found.

#define DISPLAY_VSYNC_POLARITY 0

#define DISPLAY_HSYNC_POLARITY 0

#define DISPLAY_CLOCK_POLARITY 0

#define DISPLAY_DATA_POLARITY 0

#define DISPLAY_DATA_ENABLE_POLARITY 1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

it doesn't change anything when i did as what you said. it still like this:

i am trying uboot-2015.04(on branch imx_v2015.04_4.1.15_1.0.0_ga), how can i enable split mode in uboot-2015.04?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear all,

can anybody help me? how can i solve this problem?

fulinux.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How about your hardware connection?

Do you just used three pair of LVDS data lane? If so, you should set "#define DISPLAY_IF_BPP 24 " to 18.