- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: ksz8081 probed but not auto detected on imx8m nano

ksz8081 probed but not auto detected on imx8m nano

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ksz8081 probed but not auto detected on imx8m nano

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

We have a customized imx8mn board that uses ksz8081 as an ethernet PHY chip.

We can successfully probe the PHY chip with the following kernel print:

Micrel KSZ8081 or KSZ8091 30be0000.ethernet-1:02: attached PHY driver [Micrel KSZ8081 or KSZ8091] (mii_bus:phy_addr=30be0000.ethernet-1:02, irq=77)

However, there is no auto-detected like "ADDRCONF(NETDEV_UP): eth0: link is not ready/link becomes ready" when cable plug-in.

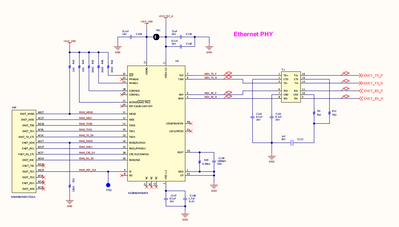

Following is the schematic of phy connection:

I have two questions :

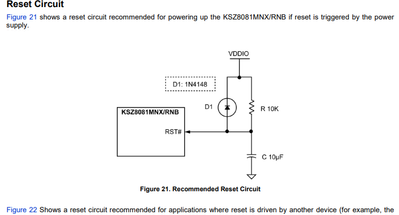

1. Here we just pull high the RST pin of ksz8081. Is that correct? Here we think the PHY chip will get rested when power on according to mircon datasheet. Although, we find most people controlled this pin with gpio.

2. Is that correct to use MX8MN_IOMUXC_ENET_TD2_ENET1_TX_CLK and do we need any modification of the clock source inside the device tree, like using PLL2_50M? (since here I see someone are using an external oscillator).

3. Is there any other place not properly implemented?

following is the device tree we used:

pinctrl_fec1: fec1grp {

fsl,pins = <

MX8MN_IOMUXC_ENET_MDC_ENET1_MDC 0x3

MX8MN_IOMUXC_ENET_MDIO_ENET1_MDIO 0x3

MX8MN_IOMUXC_ENET_TD2_ENET1_TX_CLK 0x4000001f /* ref_clk */

MX8MN_IOMUXC_ENET_TD1_ENET1_RGMII_TD1 0x1f

MX8MN_IOMUXC_ENET_TD0_ENET1_RGMII_TD0 0x1f

MX8MN_IOMUXC_ENET_RD1_ENET1_RGMII_RD1 0x91

MX8MN_IOMUXC_ENET_RD0_ENET1_RGMII_RD0 0x91

MX8MN_IOMUXC_ENET_RX_CTL_ENET1_RGMII_RX_CTL 0x1f

MX8MN_IOMUXC_ENET_TX_CTL_ENET1_RGMII_TX_CTL 0x91

MX8MN_IOMUXC_ENET_RXC_ENET1_RX_ER 0X1f

>;

};

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_fec1>;

phy-mode = "rmii";

phy-handle = <ðphy0>;

//phy-reset-gpios = <&pca9450 0 GPIO_ACTIVE_LOW>;

//phy-reset-duration = <10>;

//phy-reset-post-delay = <150>;

fsl,magic-packet;

status = "okay";

mdio {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@2 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <2>;

};

};

};

fec1: ethernet@30be0000 {

compatible = "fsl,imx8mn-fec", "fsl,imx8mq-fec", "fsl,imx6sx-fec";

reg = <0x30be0000 0x10000>;

interrupts = <GIC_SPI 118 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 119 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 120 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clk IMX8MN_CLK_ENET1_ROOT>,

<&clk IMX8MN_CLK_ENET1_ROOT>,

<&clk IMX8MN_CLK_ENET_TIMER>,

<&clk IMX8MN_CLK_ENET_REF>,

<&clk IMX8MN_CLK_ENET_PHY_REF>;

clock-names = "ipg", "ahb", "ptp",

"enet_clk_ref", "enet_out";

assigned-clocks = <&clk IMX8MN_CLK_ENET_AXI>,

<&clk IMX8MN_CLK_ENET_TIMER>,

<&clk IMX8MN_CLK_ENET_REF>,

<&clk IMX8MN_CLK_ENET_TIMER>;

assigned-clock-parents = <&clk IMX8MN_SYS_PLL1_266M>,

<&clk IMX8MN_SYS_PLL2_100M>,

<&clk IMX8MN_SYS_PLL2_125M>;

assigned-clock-rates = <0>, <0>, <125000000>, <100000000>;

fsl,num-tx-queues = <3>;

fsl,num-rx-queues = <3>;

stop-mode = <&gpr 0x10 3>;

fsl,wakeup_irq = <2>;

status = "disabled";

};

Thanks for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jie

>1. Here we just pull high the RST pin of ksz8081. Is that correct?

seems more correct is to use Figure 21 option.

>2. Is that correct to use MX8MN_IOMUXC_ENET_TD2_ENET1_TX_CLK..

yes, also may be recommended to check direction, configured in uboot as in setup_fec() example

below

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Igor

Thanks for your quick reply. And truly appreciate your help again.

Here I am a little confusing. Since I am not going to use an ethernet connection inside the u-boot. Do I still need to configure the PIN configuration and the clock source inside the U-boot?

Thanks,

Jie

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

setup_fec() shows configuration IOMUXC_GPR_GPR1 (bit GPR_ENET1_TX_CLK_SEL),

clock direction, described in sect.8.2.4.2 General Purpose Register 1 (IOMUXC_GPR_GPR1),

i.MX 8M Nano Applications Processor Reference Manual

so it should be configured properly somewhere.

Best regards

igor