- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

imx6ul.the dts about the weim

hi

i went to use the weim driver,but i dont't know who to config the dts.

the kernel document have gave a Example:(kernel-source\Documentation\devicetree\bindings\bus\imx-weim.txt).

Example for an imx6q-sabreauto board, the NOR flash connected to the WEIM:

weim: weim@021b8000 {

compatible = "fsl,imx6q-weim";

reg = <0x021b8000 0x4000>;

clocks = <&clks 196>;

#address-cells = <2>;

#size-cells = <1>;

ranges = <0 0 0x08000000 0x08000000>;

nor@0,0 {

compatible = "cfi-flash";

reg = <0 0 0x02000000>;

#address-cells = <1>;

#size-cells = <1>;

bank-width = <2>;

fsl,weim-cs-timing = <0x00620081 0x00000001 0x1c022000

0x0000c000 0x1404a38e 0x00000000>;

};

};

mine :

weim: weim@021b8000 {

compatible = "fsl,imx6ul-weim", "fsl,imx6q-weim";

reg = <0x021b8000 0x4000>;

interrupts = <GIC_SPI 14 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clks IMX6UL_CLK_EIM_SLOW_PODF>;

}; //int the imx6ul.dtsi

&weim {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_weim>;

#address-cells = <2>;

#size-cells = <1>;

status = "okay";

ranges = <0 0 0x50000000 0x08000000>;

imx-weim@0,0 {

compatible = "imx-weim";

reg = <0 0 0x02000000>;

#address-cells = <1>;

#size-cells = <1>;

bank-width = <2>;

fsl,weim-cs-timing = <0x403304b1 0x00000001 0x0f010000

0x00000008 0x0f040040 0x00000000>;

};

}; //in the imx6ul-14x14-evk.dts

pinctrl_weim: weimgrp {

fsl,pins = <

MX6UL_PAD_CSI_MCLK__EIM_CS0_B 0x10b0

MX6UL_PAD_CSI_PIXCLK__EIM_OE 0x10b0

MX6UL_PAD_CSI_VSYNC__EIM_RW 0x10b0

MX6UL_PAD_LCD_DATA08__EIM_DATA00 0x1b0b0

...

....

>;

}; //in the imx6ul-14x14-evk.dts

but i can't read the register and ioremap the weim memory.

tolt me i can check the CCM register CCM_CCGR6 . imx6ul:help,i can't read or write the weim register.

when i changed the value ,i can read and write the memory.

thanks again .

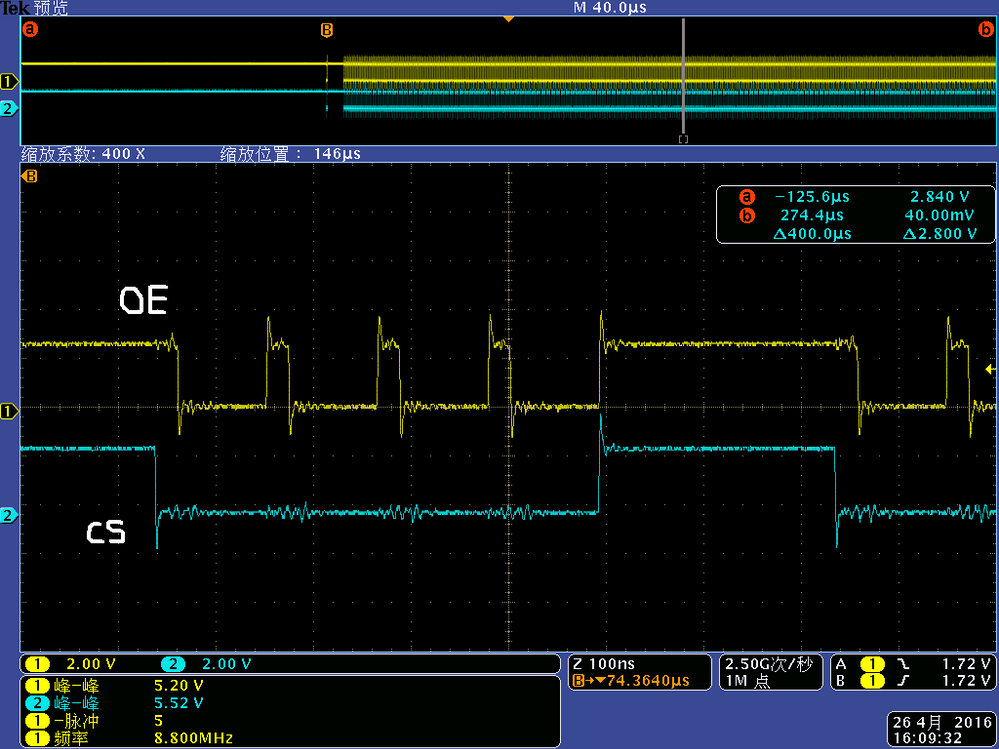

but wen i use the oscilloscope to check the wei.cs0 、wei.oe 、wei.rw

No matter how many times to read ,they only change once ,and can't read or write the real value.

In my mind,if the kernel afford the driver ,i only change the dts if i want to use the driver .for example the ecspi ,i2c driver. but in this mode ,i can't read the memory if i didn't change the CCM register CCM_CCGR6 .

i thank it's not the normal way to use this driver.

i can't find any more information form the kernel except the Example for an imx6q-sabreauto board(kernel-source\Documentation\devicetree\bindings\bus\imx-weim.txt).

Some people tolt me i only to config the dts.and ioremap the 5000_0000 memory phy_adr to read and write.

but i don't know how to config the dts in right way.

the Example in the kernel Documentation is right?

why i have to config the CCM register CCM_CCGR6 even i have configed the dts Modelled on the Example ,if i want to read or write the memory.

Thank you for attention!!

Hi Yi

I think it is not possible to enable CCM_CCGRn in dts, however

one can try to set it in dcd header (uboot *.cfg init file)

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi igor

sorry ,i don't know who to find the dcd header,but i know the problem may be in tne kernel .

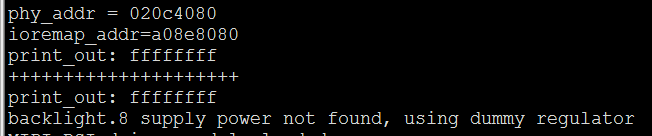

i modify the weim driver,add same debugging information:

#define CLK_register 0x20C4080

struct resource *my_mem ;

int offset = 0;

printk("offset = %d\n",offset);

my_mem = request_mem_region(CLK_register + 0x4000 * offset, 0x4000, "testPF");

if (my_mem == NULL) {

printk("failed to get memory region\n");

return -ENOENT;

} else

printk("phy_addr = %08x\n",CLK_register + 0x4000 * offset);

void __iomem *plx_membase ;

plx_membase = ioremap(CLK_register + 0x4000 * offset, 0x4000);

if(NULL == plx_membase) {

printk("ioremap error\n");

}

printk("ioremap_addr=%lx\n",(u_long)plx_membase);

printk("print_out: %08x\n",readl(plx_membase));

printk("+++++++++++++++++++++\n");

unsigned int ret_val = readl(plx_membase);

ret_val = ret_val | ( 0x3 << 10);

writel(ret_val ,plx_membase);

printk("print_out: %08x\n",readl(plx_membase));

iounmap(plx_membase);

release_mem_region(CLK_register + 0x4000 * offset,0x4000);

when the board staring:

but after logo ,the CCM register CCM_CCGR6 have been modified.and i can't read or write the weim register......

by other way,i can use the weim by using my driver to init the CCM register CCM_CCGR6.

ioremap the phy_adr by " /dev/mem."

and it work well.

how can i find the clk init function?

thanks!