- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- imx6ULL RTS signal

imx6ULL RTS signal

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

imx6ULL RTS signal

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi All,

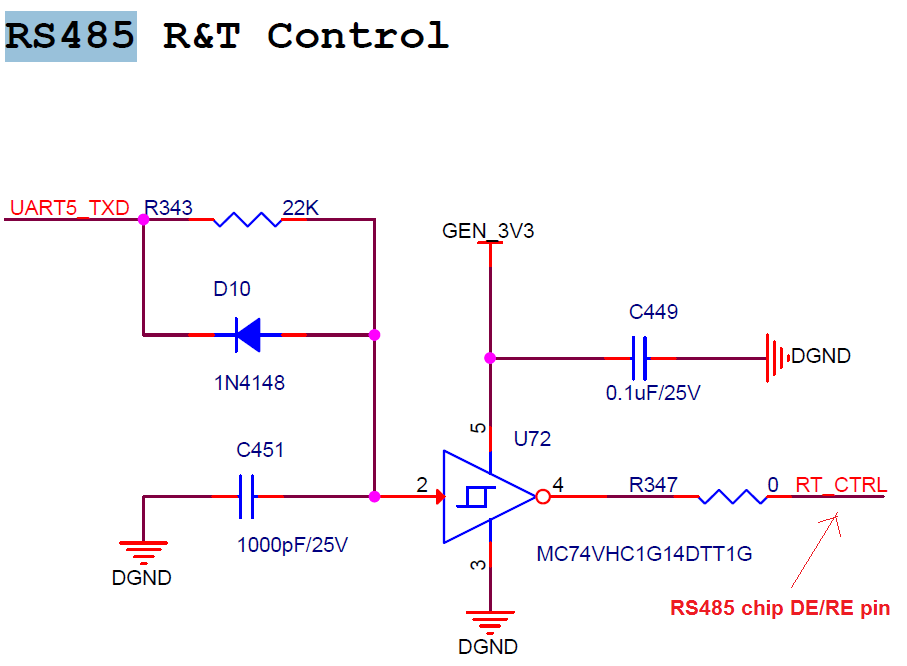

We are using the imx6ULL processor MCIMX6Y2CVM05AA and RS485 transceiver IC ST485BDR in our design.We are facing a similar issue related to RS485 RTS signal as above.We are using the UART port 2 of the processor ( UART2_TX transmit function,UART2_RX for receive function,UART3_RXD pin for TX enable and RX enable of RS485 transceiver).We are using kernel version 4.1.x.x.

We were able to toggle the RTS line of UART2 by configuring it as a GPIO line but we are missing few bytes and not able to receive the complete data.

The transit enable from ULL processor is not going low immediately after the transmission is completed( Highlighted in green in attachment). We are losing few bytes as the delay between the Rx enable and Rx data is very small (Highlighted in Red in attachment).

How to make the RTS signal low immediately after the transmission is over ?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Roshan,

In DCE mode, UART_CTS is used to control data IO directions, you multiplexed RTS to be GPIO and used it to control TX/RX , exactly, which will cause data to be lost. Because you don't know when TX / RX is done. RS485 is half-duplex communication.

For RS485 design, I have 3 suggestions for you :

1. Using UART CTS to control IO direction of data.

This is supported by UART IP, you can find the function in i.MX6UL Reference manula.

2. Using Hardware control it, don't need any code in software.

3. Using GPIO to control DE/RE#

Since you used GPIO to do it, I think you should check the "empty interrupt" of UART TX FIFO , if the interrupt occurs, GPIO should be switched to RECEIVE (maybe pull it down to LOW)

Have a nice day!

NXP TIC weidong sun