- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

Hi community,

We want to know about i.MX6SDL IPU parallel display port.

[Q1]

We understand IPU parallel display port can output display data which is compliant to ITU-R BT.601 since it supports BT.656 & BT1120, is this correct?

[Q2]

Can i.MX6SDL IPU parallel display port output display data which is compliant to VESA DMT standard timing also?

Our concern is that whether i.MX6SDL can generate the aprepriate frequency for the pixel clock.

I understand the source clock of the pixel clock is PLL3 PFD1 as default setting.

In this case, PLL3 PFD1 is used for only display modules (IPU, EPDC, HDMI).

So I believe PLL3 PFD1 does not affect other than display modules even if the output frequency is changed and i.MX6SDL can output VESA DMT standart data.

Is this correct?

Best Regards,

Satoshi Shimoda

已解决! 转到解答。

Hi Satoshi

1. correct

2. correct, also BSP calculates the timings using VESA, as states

MX53UG Chapter 18 Table 18-3. Parameter Information

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Satoshi

1. correct

2. correct, also BSP calculates the timings using VESA, as states

MX53UG Chapter 18 Table 18-3. Parameter Information

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Igor,

Thank you for your reply.

Then, I found the document about the parameter in <linux dir>/Documentation/fb/modedb.txt (There is same file in L3.0.35_4.1.0 and L3.10.17_1.0.0-ga).

And I tried VESA output to MCIMX51LCD with L3.0.35_4.1.0 and L3.10.17_1.0.0-ga.

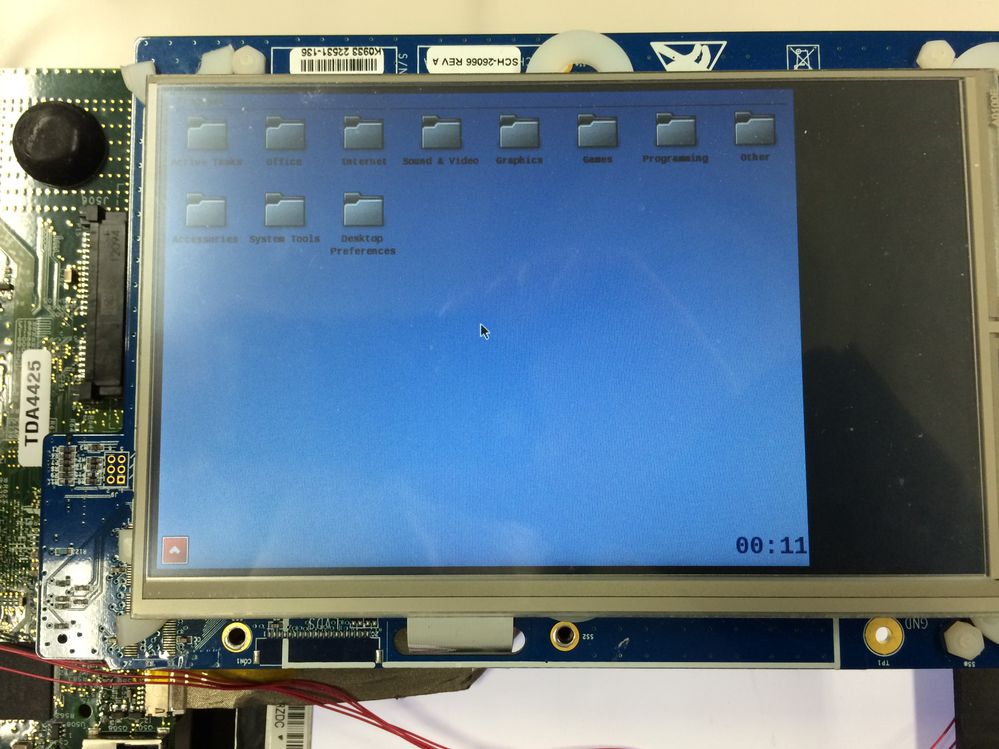

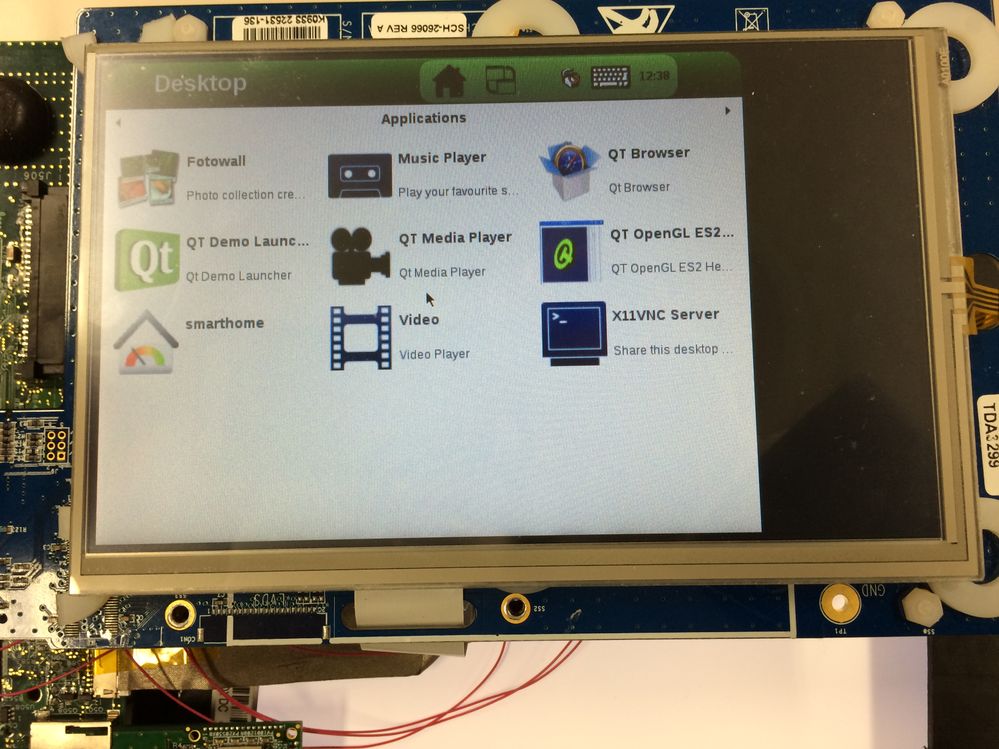

The results are the following pictures, these seem good.

In this case, I used the following bootargs.

[L3.0.35_4.1.0]

bootargs_mmc=setenv bootargs ${bootargs} root=/dev/mmcblk1p1 rootwait rw video=mxcfb0:dev=lcd,640x480M-16@55,if=RGB565

(@60 generated flicker)

[L3.10.17_1.0.0-ga]

bootargs_mmc=setenv bootargs ${bootargs} root=/dev/mmcblk0p1 rootwait rw video=mxcfb0:dev=lcd,640x480M-16@60,if=RGB565

Thank you for your great support.

Best Regards,

Satoshi Shimoda