- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: (i.MX28) How can we improve the waveforms of EMI?

(i.MX28) How can we improve the waveforms of EMI?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Community,

We are having a problem with the waveforms of EMI of i.MX28.

There are overshoots/undershoots which are more than 300mV on Address/Command signals.

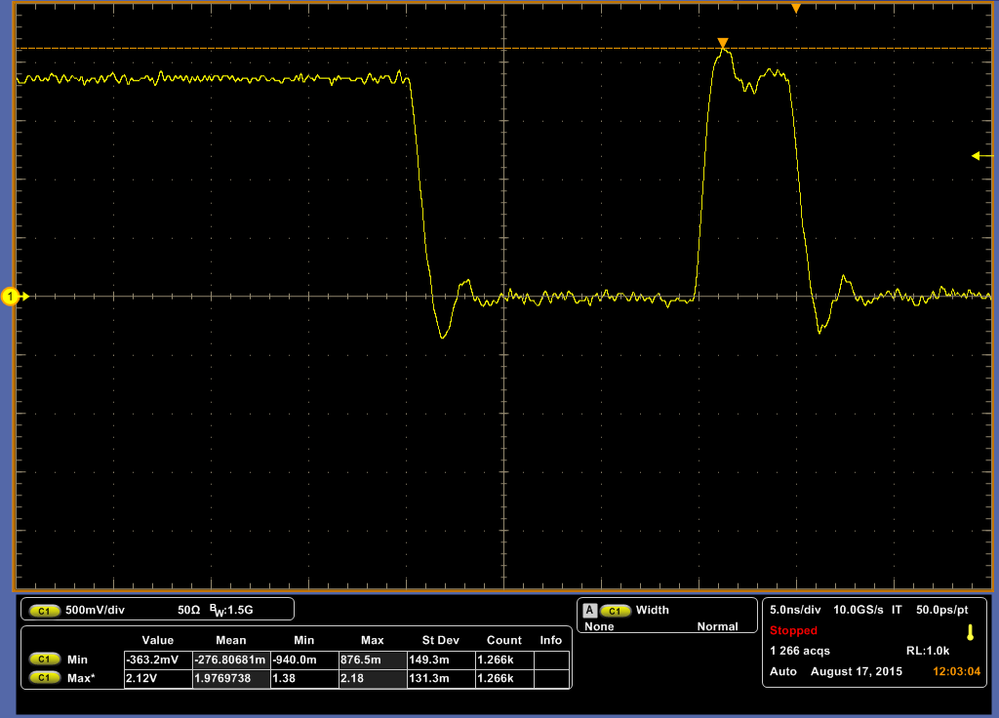

The image is A6 probed at a via near DDR2.

Are there any way to reduce the shoots from Address/Command without modifying hardware?

The conditions of our board are as follows:

-The board is 6-layer.

-The pattern length of each EMI line is 30.2-34.0mm.

-There are no dumping resistors on the Address/Command line.

-The only register settings which is modified from the reset value is bit 1 of EMRS(1), or HW_DRAM_CTL183. (Reducing the drive strength of DDR2.)

-Adding dumping registers to the Address/Command lines are too risky.

The board is our original design and the pattern of EMI is not copied from EVK since our board is too small to do so.

Instead we simulated the pattern before manufacturing the board and the result was that the overshoots and undershoots are less than 300mV.

Since the vias we used to probe were a little apart from the balls of DDR2, the shoots are not as bad as it seems at the balls.

But as there is no way to observe the exact waveform at the ball, we'd like to improve the waveform we can see.

Thank you,

Hikaru

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Try to play with the ODT and drive strength settings of the i.MX28 EMI signals

in the HW_PINCTRL_EMI_ODT_CTRL and HW_PINCTRL_EMI_DS_CTRL registers of the

i.MX28 Pin Control (PINCTRL) module.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Try to play with the ODT and drive strength settings of the i.MX28 EMI signals

in the HW_PINCTRL_EMI_ODT_CTRL and HW_PINCTRL_EMI_DS_CTRL registers of the

i.MX28 Pin Control (PINCTRL) module.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Artur,

Thank you for your reply.

Since the reset value of the drive strength is the lowest, I don't think changing the setting reduces the shoot.

As for the ODT, I thought the ODT is used when there are 2 or more RAMs...

Is there any settings you recommend, or should we find the optimum setting by trial and error?

Thank you,

Hikaru

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The issue is very design dependent, so, no strict recommendations can be done. Just try to play with the settings.

Best Regards,

Artur

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Artur,

Thank you for the advice.

We will try ODT.

Best regards,

Hikaru

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Artur,

By enabling the ODT, we could reduce the undershoots on the address/command signals.

However the worst value of the shoots still exceed 300mV, it's less than 500mV now.

In our case, the results of TLOAD 50 ohm and 75 ohm was almost same. Both cases resulted in reduced undershoots. ODT calibration didn't make significant difference.

Best regards,

Hikaru Uruno