- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: i.MX 8M Family DDR Tool LPDDR4 32 Bit Bus Width Calibration Error

i.MX 8M Family DDR Tool LPDDR4 32 Bit Bus Width Calibration Error

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello everyone,

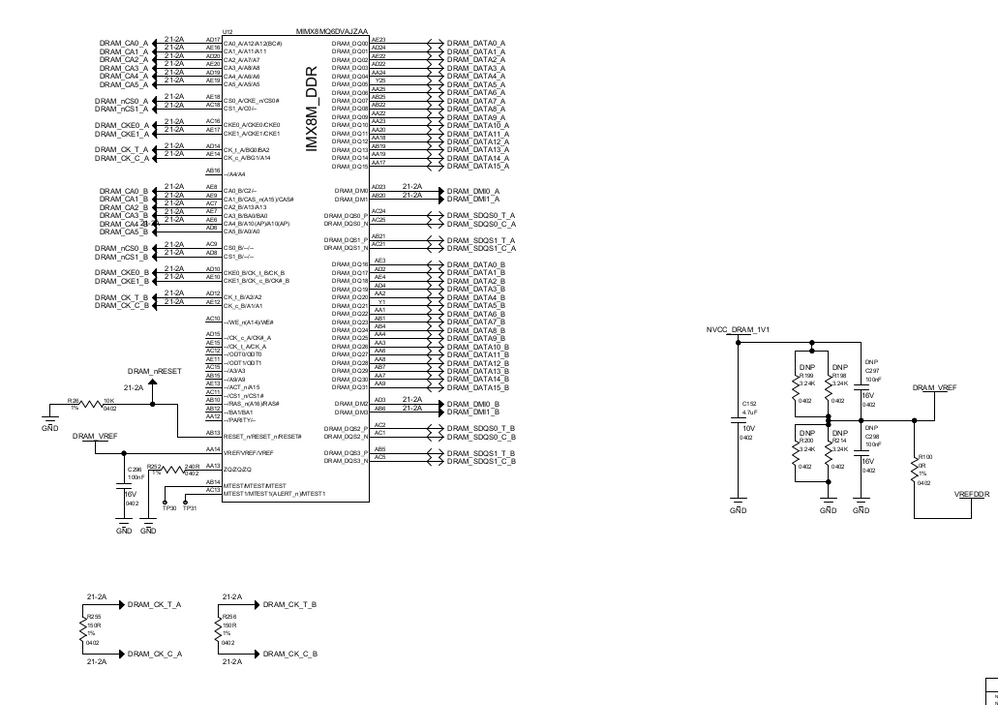

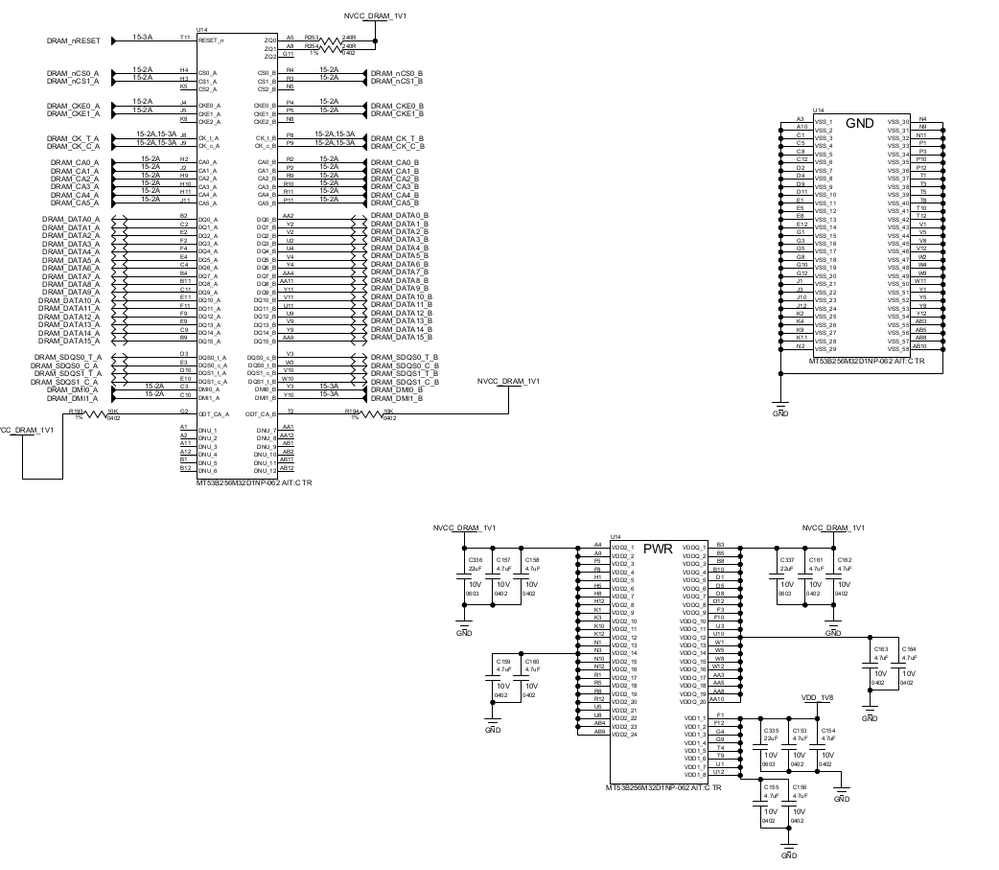

We have designed a custom board with i.MX 8M Quad CPU. We controlled the voltages and clocks on the board. We are using "MT53B256M32D1NP" as LPDDR4 on board which is connected 32 bits bus width. Our boards MT53B256M32D1NP's layout information is given in attachment "ddr_specs.jpg" and DDR Controller Configuration Aid Spreadsheet configuration (RPA) based on MXM8M_LPDDR4_RPA_v24.xlsx is given in attachment "ddr_aid_cfg.jpg" and i.MX side connection schematic is given in attachment ddr_sch.jpg.

When we download the ds file to the board and then run calibration using DDR tool, the tool prints:

Downloading file 'bin\lpddr4_train1d_string.bin' ..Done

Downloading file 'bin\lpddr4_train2d_string.bin' ..Done

Downloading file 'bin\lpddr4_pmu_train_1d_imem.bin' ..Done

Downloading file 'bin\lpddr4_pmu_train_1d_dmem.bin' ..Done

Downloading file 'bin\lpddr4_pmu_train_2d_imem.bin' ..Done

Downloading file 'bin\lpddr4_pmu_train_2d_dmem.bin' ..Done

Downloading IVT header...Done

Downloading file 'bin\m850_ddr_stress_test.bin' ...Done

Download is complete

Waiting for the target board boot...

********Found PMIC PF0100**********

*************************************************************************

*************************************************************************

*************************************************************************

MX8 DDR Stress Test V3.10

Built on Feb 5 2020 14:08:44

*************************************************************************

--Set up the MMU and enable I and D cache--

- This is the Cortex-A53 core

- Check if I cache is enabled

- Enabling I cache since it was disabled

- Push base address of TTB to TTBR0_EL3

- Config TCR_EL3

- Config MAIR_EL3

- Enable MMU

- Data Cache has been enabled

- Check system memory register, only for debug

- VMCR Check:

- ttbr0_el3: 0x91d000

- tcr_el3: 0x2051c

- mair_el3: 0x774400

- sctlr_el3: 0xc01815

- id_aa64mmfr0_el1: 0x1122

- MMU and cache setup complete

*************************************************************************

ARM clock(CA53) rate: 800MHz

DDR Clock: 1600MHz

============================================

DDR configuration

DDR type is LPDDR4

Data width: 32, bank num: 8

Row size: 15, col size: 10

One chip select is used

Number of DDR controllers used on the SoC: 1

Density per chip select: 1024MB

Density per controller is: 1024MB

Total density detected on the board is: 1024MB

============================================

MX8M: Cortex-A53 is found

*************************************************************************

============ Step 1: DDRPHY Training... ============

---DDR 1D-Training @1600Mhz...

[Process] End of CA training

[Process] End of initialization

PMU: Error: RxEn training preamble not found

PMU: ***** Assertion Error - terminating *****

[Result] FAILED

If we change the bus witdh to 16 using RPA then the calibration is done successfully but the density of DDR is shown as 512MB as expected.

We could not found our problem. What causes "PMU: Error: RxEn training preamble not found" error? What can do after this point? Any help appreciated.

Best regards

Onur

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We have reviewed the your RPA and no problem is found.

From your description, there is something wrong in channel B of LPDDR4. Please go to check the hardware connection on LPDDR4 channel B.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Rita,

Thank you very much for your help. By your help we see the problem. Our hardware guys had entered the symbology of DDR's channel pins in different order in DDR connections.

Thanks for your precious time.

Have a nice day.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

You are welcome~~

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Onur,

Could you send us your the customized Programming Aids, LPDDR4 datasheet and the DDR connection pictures. And then we will do further confirm it for you.

Have a nice day

Rita

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Rita,

Thank you for your interest.I am sorry to inform you that I can not share datasheet of MT53B256M32D1NP because of NDA concerns. But I think I can share the link of datasheet of MT53B256M32D1NP which is "http://files.pine64.org/doc/datasheet/rockpro64/SM512M32Z01MD2BNP(200BALL).pdf ".

I am attaching the i.MX8MQ (m850) DDR Controller Configuration Spreadsheet that I customized. And the LPDDR4 connection pictures of the schematics of our board.

I can not attach the spreadsheet directly so I am sending the link that I shared the spreadsheet.

Filebin :: bin 2adcq1nmmh5q89pr

Best regards.

Onur

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We have reviewed the your RPA and no problem is found.

From your description, there is something wrong in channel B of LPDDR4. Please go to check the hardware connection on LPDDR4 channel B.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I will confirm it for you. Please wait.