- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

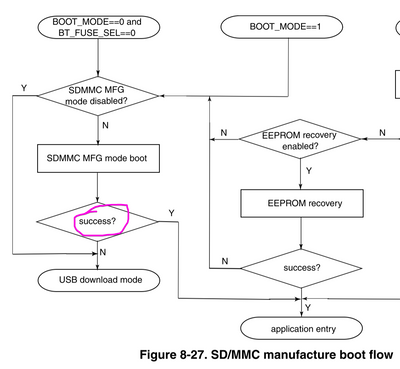

From the above figure from the reference manual, what are the likely causes for the SDMMC check failing? I soldered up three copies of a new revision of a board that was previously booting without issue, and all three of them refuse to boot into U-Boot from an SD card via SD/MMC Manufacture Mode.

Probing the SD/MMC bus shows activity on CMD and then DAT1 (1-bit SD mode, as mentioned in the datasheet) for approximately 175 ms:

This is identical to the behavior on a good board. But right after this is completed, the board will jump to the USB bootloader.

I'm wondering if my RAM didn't quite reflow properly — but it seems strange to have the same problem with all three boards.

Any other things I should check? The difference between board revisions is only some low-speed GPIO signals getting moved around, which shouldn't affect any of this, so from U-Boot's perspective, they should look identical to the last revision.

已解决! 转到解答。

Found the problem! Apparently, the 2V5 regulator net got renamed between versions, and the corresponding DRAM supply pin still had the old name, so they were disconnected. Soldered a wire between the two nets and we're back in business!

Hi jay2

for SDMMC boot failing may be recommended to run ddr test

then rebuild uboot with new calibration settings found from ddr test, put them in dcd header:

DCD is described in sect.8.7.2 Device Configuration Data (DCD)

i.MX 6ULL Applications Processor Reference Manual

Best regards

igor

Good call! I completely forgot about that tool. Sure enough, there's something really screwed up with my DDR3L. All three boards I'm testing all report all 1's on the data right at the first address 0x80000000.

I noticed that on good boards, DDR_RESET de-asserts (goes high) as soon as I download the script. On the bad boards, it never de-asserts. This is a problem across all three boards. I checked the pull-down resistor and it's 10k. There's no short to GND on the signal.

If I force the DDR_RESET signal high to take the DRAM out of reset and then re-run the stress-test tool, I get the same failure.

Any ideas?

Found the problem! Apparently, the 2V5 regulator net got renamed between versions, and the corresponding DRAM supply pin still had the old name, so they were disconnected. Soldered a wire between the two nets and we're back in business!