- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

What is the Base Address of the GIC and Is it controlled by the SCU unit or not?

Hello,

I couldn't found the GIC Base_ Address in the Memory Map chapter. so Is that mean that any peripheral that it's base address is missing from the memory map chapter is controlled by the SCU unit or else?

Hi Igor

The RM you use is for i.MX 8QuadMax but I'm using i.MX 8QuadX

Hi Helmy

for i.MX8X one can look at dts:

gic: interrupt-controller@51a00000

fsl-imx8dx.dtsi\freescale\dts\boot\arm64\arch - linux-imx - i.MX Linux kernel

Best regards

igor

Hi Igor

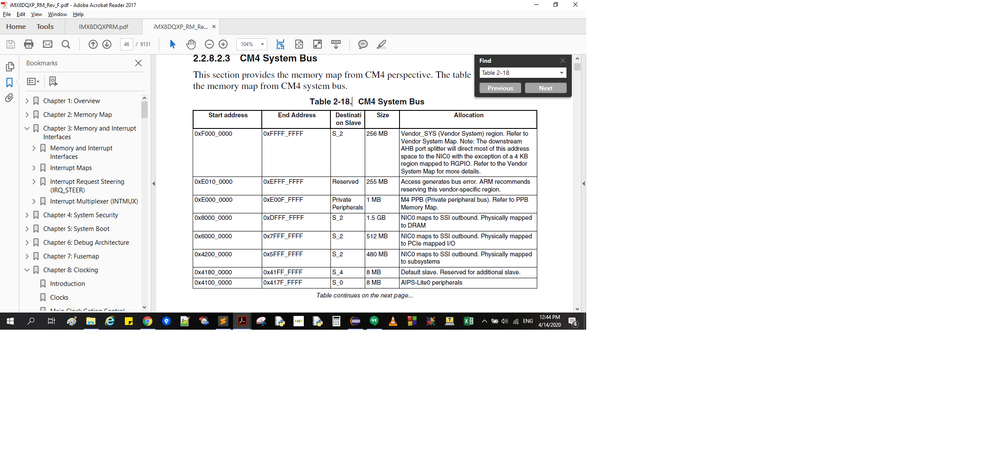

I can't found the base address for the GIC in the Table that you've mentioned. I've looked up the TRM table 2 - 18 didn't found anything.

Also nothing in the DB memory map regarding the Address you've sent.

Also If there is any peripherals with missing Base_Addresses in the TRM should I Assume that it's controlled by the SCU unit

Hi Helmy

GIC address is 51A0_0000 according to Table 2-18. Dblog memory map

i.MX8QM Reference Manual (one can obtain it in local marketing office).

Yes it is controlled by the SCU and described in

sect.13.1 (SVC) Interrupt Service sc_fw_api_qm_b0.pdf included

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------