- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Reset i.MX6Q without resetting PF0100

Reset i.MX6Q without resetting PF0100

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Reset i.MX6Q without resetting PF0100

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Champs,

I'd like to reset i.MX6Q without resetting PF0100 and implemented the design.

However when only i.MX6Q is reset, we got lower VDDARM_IN output(about 960mV) from PF0100.

I guess thanks to DVFS, i.MX6Q can operate in lower frequency and lower voltage.

When i.MX6Q is reset in such situations, PF0100 continues to provide the lower voltage even though i.MX6Q needs more voltage in reset. Is this correct understanding?

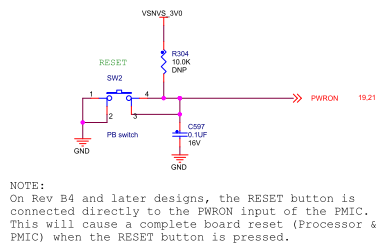

I found reset(SW2) is directly connected to PMIC in the current SabreSD design.

I also found the following design in the old SabreSD schematics.

From the NOTE, there seems to have been troubles resetting i.MX6Q without getting reset de-asserted from the PMIC.

What's the issue?

Is it possible to create a design that only resets i.MX6Q but resets PF0100?

Best regards,

Nori Shinozaki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

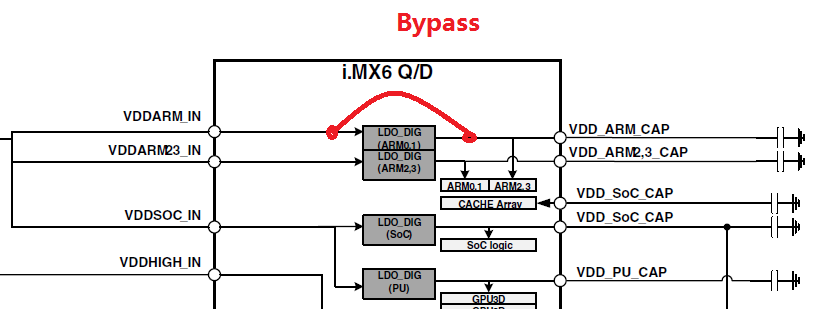

If you use the ldo enable mode, you can reset i.MX6 alone safely, with AND without DVFS.

Because ldo enable mode is using the internal PMU, so the PMIC that time like a discrete power supply.

The i.MX6 is using the PMU to change the voltage. Not any change to PMIC.

The input on VDDARM_IN and VDD_SOC_IN is fixed not dynamic like a discrete power supply.

If you ldo bypass mode, the internal PMU is not working. It is bypass.

So the i.MX6 has to use the i2c to control the pmic the change the voltage.

The input on VDDARM_IN and VDDSOC_IN is dynamic.

If that time, the voltage is changed to like power save mode, and the i.MX6 is bootup at configuration 800M.

It may cause the problem. Of course, the reason is not that simple, maybe other peripherals will also effect the reboot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Suggest you use the ldo enable mode and you can keep the dvfs enable.

When you use ldo enable mode, the dfvs is working with internal pmu. You can still use that feature.

Using internal pmu(ldo enable mode) is very close to using dicrete power supply.

In ldo bypass mode, the dvfs is using i2c to control the pmic to adjust the voltage.

In some situation, during the adjusting the voltage, the reset is happenning.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Biyong,

I see!

As long as we use LDO Enable mode, we can reset i.MX6 alone safely, with or without DVFS.

Besides, we can avoid I2C failure on rest!

Thanks & BR,

N.S.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If you use the wdog1, it will reset i.MX6 without reset PMIC.

You can refer to the following link.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Biyong,

Now I understood all I need to change is:

# Disable DVFS

operating-points =<...>;

fsl,soc-operating-points = <...>;

# Reset without reset PMIC

fsl,ldo-bypasst = <1>;

fsl,wdog-reset = <1>;

Thanks & BR,

N.S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I agree with Your approach.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks,

We will try.

Best regards,

NS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

generally You idea, that PMIC voltage can stay in recent state because

of DVFS is quite reasonable. IMX6 after reset cannot change PMIC voltages

itself, if recent PMIC voltages are not proper for power up. To check it, please

try any bare metal test code, which does not influence on PMIC voltages.

Under Linux - it makes sense to disable DVFS for Your PMIC configuration.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Yuri,

I looked for PlatformSDK but I couldn't find relevant sources.

Then I looked for unit_tests/imx-test and found a file FSL-UT-PM-006.txt which says:

| Test Procedure |

.To Enable DVFS:

echo 1 > /sys/devices/platform/imx_dvfscore.0/enable

.To Disable DVFS:

echo 0 > /sys/devices/platform/imx_dvfscore.0/enable

However I couldn't find the imx_dvfscore.0 directory in the latest Yocto BSP(3.14.52) filesystem

Then I looked for a clue in the BSP sources and found out a kernel config CONFIG_PM_DEVFREQ.

Can we disable DVFS just by setting CONFIG_PM_DEVFREQ=n in kernel configs?

Because I found Vivante GPU, MMDC, USB and etc also have registers themselvs to enable or disable DVFS.

P.S. Please try to find why they change SabreSD design how to reset.

Best regards,

Nori Shinozaki

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The following may help regarding DVFS : i.MX6 :: Disabling DVFS in kernel configuration

~Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yuri,

The URL is for NXP personnel only.

Now disabling DVFS equals to fix cpu frequency by cpufreq written in Linux RM below?

Chapter 24

CPU Frequency Scaling (CPUFREQ) Driver

BR,

N.S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have sent the information under case 00078289.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yuri,

Very thanks!

After reading the thread, I found your suggestion is the simple & best

solution.

My customer likes to reset i.MX6 only(no PF0100) in LDO Bypass fixed at

792MHz@1.275V

In that case, they just need to set as follows, correct?

imx6q.dtsi

operating-points = <

/* kHz uV */

792000 1275000

>;

fsl,soc-operating-points = <

/* ARM kHz SOC-PU uV */

792000 1275000

BTW, do they also need to disable MMDC auto self-refresh as written in

this thread?

https://community.nxp.com/thread/307212

Best regards,

Nori Shinozaki

2016-06-01 14:06 GMT+09:00 Yuri <admin@community.freescale.com>:

<https://community.nxp.com/>

Reset i.MX6Q without resetting PF0100

reply from Yuri Muhin

<https://community.nxp.com/people/Yuri?et=watches.email.thread> in *i.MX

Community* - View the full discussion

<https://community.nxp.com/message/656328?et=watches.email.thread#comment-656328>

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As for configuring operating points in device tree file - I think it would be better

to preserve original number of working points, but just let they are the same.

Memory auto-refresh may be needed only if it is needed to preserve previous

content, without memory initialization.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yuri,

Like this?

operating-points = <

/* kHz uV */

792000 1275000

792000 1275000

792000 1275000

792000 1275000

792000 1275000

>;

fsl,soc-operating-points = <

/* ARM kHz SOC-PU uV */

792000 1275000

792000 1275000

792000 1275000

792000 1275000

792000 1275000

>;

BR,

N.S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yuri,

Besides disabling DVFS, three possible solutions came up to my mind for how to reset i.MX6Q only.

1. Fix the frequency in cqufreq

2. Use internal LDO and let PMU controls DVFS

3. Use Warm reset or Watchdog reset in i.MX6Q

What do you think?

Best regards,

Nori Shinozaki