- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Re: 3 Wire SPI Working

Hello Mohammed,

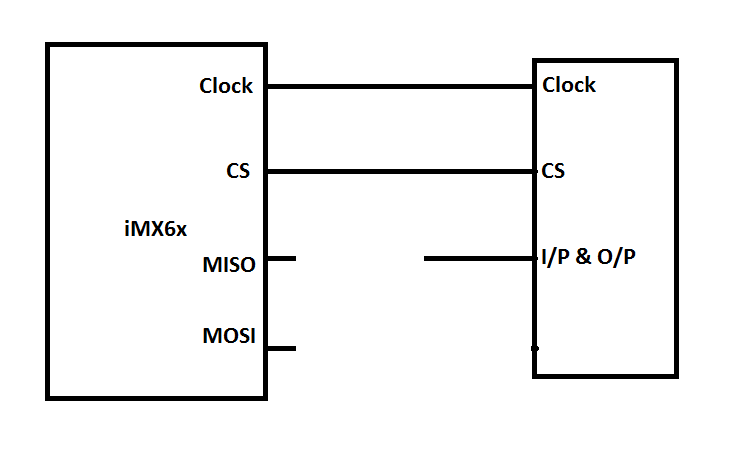

Could you tell me that, how did you connect 3-wire SPI into iMX6x processor ? The output/input line from the slave connected to which pin of processor (whether MISO or MOSI) ?

Regards,

Azlum

Dear Azlum,

I am also working on 3-Wire SPI. I read your posts. Can you clarify my doubts.

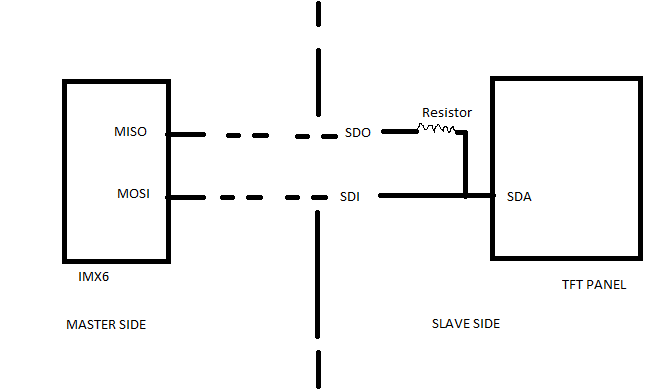

I have imx6 board with MOSI and MISO both Connected to SDI and SDO of LCD (Slave device).

On the slave side , SDO and SDI are connected together where SDO is connected via a resistor

My query is

1) How will I tell linux kernel to use SPI-3 Wire mode

2) As per your previous discussion, MOSI should be connected via a resistor.?

3) In my case MISO is connected to SDO which is connected to SDI via a resistor(different from your case). Will that work out?

4) Bitbanging is only required if I don t connect MOSI to MISO via a resistor ?

Thanks in advance

Hi Mohammad,

We have imx28 customized board. LCDIF was interfaced to 3 wire spi display panel. The input/output line from the slave connected to both the pins i.e MISO and MOSI. Even in your case it should be connected like that.

Hi Yuri,

If I configure MISO and MOSI as open drain, then the Master and Slave communication will be out of SPI protocol.

i.e, one side (Slave side) is 3-wire SPI interface and another side (Master side) is open drain interface.

Whether my statement is correct ?

Regards,

Azlum

Hi Yuri,

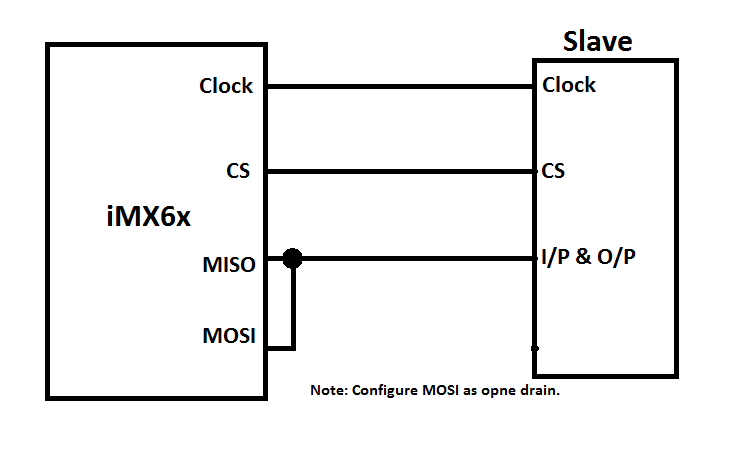

i.e iMX6 SPI MOSI and MISO short together and configure MOSI as open-drain mode. In other words, SPI with MOSI open-drain mode.

What about MISO ? No need to configure as anything ?

Based on your input I modified my wiring diagram. Can you review the same ?

Regards,

Azlum

Hello Yuri,

So iMX6x MISO and MOSI need to be shorted together and finally connect to 3-wire SPI slave bidirectional data line (I/P & O/P line). Is it like that ?

Then MOSI need to be configured as GPIO. Then what about MISO ? This pin no need to configure as anything ?

Regards,

Azlum

Assuming i.MX6 is SPI master, You may configure its MOSI output as open drain one

(via ODE bit field of corresponding IOMUXC_SW_PAD_CTL_PAD register) and

connect together i.MX6 MOSI, MISO and external SPI device I/O [I/P & O/P].

If needed, external device I/O should be configured for open drain too.

When configuring GPIO, the Processor Expert for i.MX may be useful.

http://www.freescale.com/webapp/sps/site/prod_summary.jsp?code=PROCESSOR-EXPERT-IMX

https://community.freescale.com/docs/DOC-101470

Also, the following app note helps to setup pin’s electrical properties.

“Influence of Pin Setting on System Function and Performance”

http://www.freescale.com/files/32bit/doc/app_note/AN5078.pdf

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------