- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- PMIC_ON_REQ behavior during CPU POR

PMIC_ON_REQ behavior during CPU POR

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PMIC_ON_REQ behavior during CPU POR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

We are designing a custom board using i.MX 8 DualXPlus CPU based on the i.MX 8QXP MEK board.

In order to simplify the Reset Scheme, we are doing the following changes:

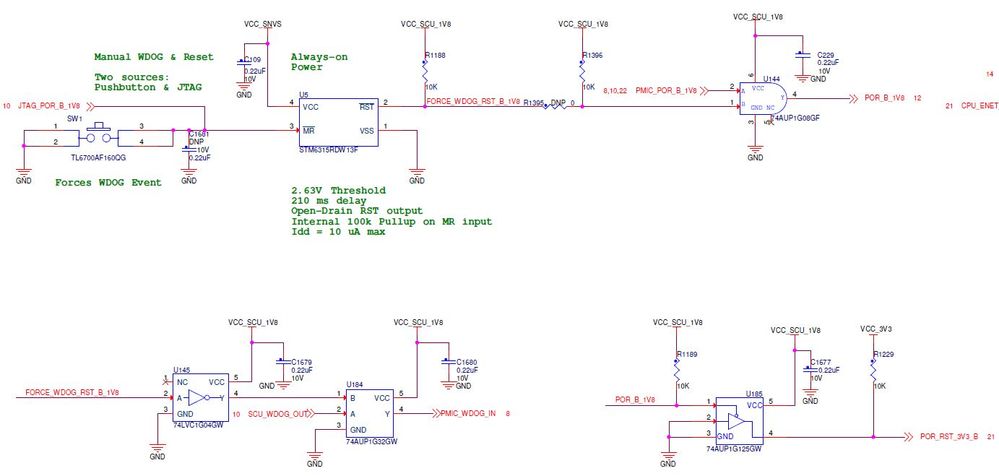

1. The SCU_WDOG_OUT and PMIC_WDOG_IN is bypassed (connected directly).

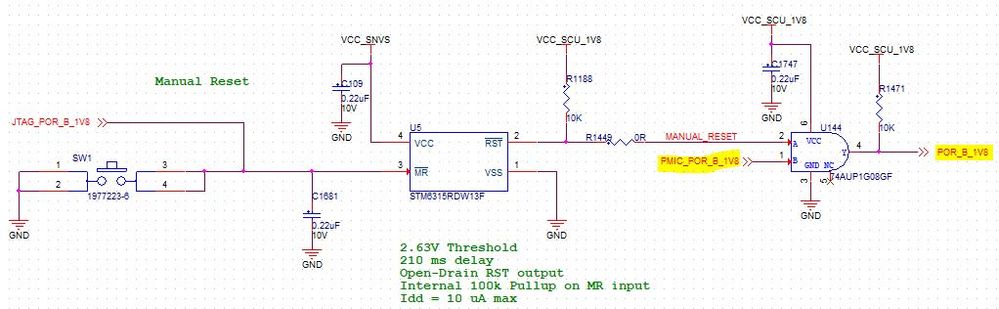

2. PMIC_POR_B_1V8 is logically ANDed with the supervisory circuit as shown in the attached image:

We have two questions:

1. In the event of pressing the manual reset button SW1, it will drive MANUAL_RESET to 0V eventually driving POR_B_1V8 to 0V so that the processor resets. During this, does the PMIC also perform a reset operation ( complete power cycle of all regulators)?

2. What will be the behaviour of PMIC_ON_REQ signal from the processor in the above event?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Harsh

1. in such connection PMIC will not perform a reset operation, because

PMIC is reset by PMIC_WDOG_IN signal.

2. behaviour of PMIC_ON_REQ signal will be unaffected.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thanks for the reply.

So if we keep the PMIC WDI signal interfacing as it is in original design:

Does this ensure a hard WD reset (reset of all voltage regulators+ reset of MCU) when we press the SW1 button?

And in the design why is R1395 kept DNP?

We are going to use the PMIC MC34PF8100FJEP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Harsh

>Does this ensure a hard WD reset (reset of all voltage regulators+ reset of MCU) when we press the SW1 button?

yes

>And in the design why is R1395 kept DNP?

PMIC_POR_B_1V8 will be produced by PMIC reset on p.8, so it is duplication.

Best regards

igor