- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: PCIe on i.mx8: Phy link never came up

PCIe on i.mx8: Phy link never came up

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

PCIe on i.mx8: Phy link never came up

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

We are trying to use PCIe on our custom i.MX8M Plus based design. Unlike EVK that has M.2 connector, we are using mini PCIe connector. We are not able to get RC device in lspci. Below are the dmesg log related to PCI:

[ 0.089490] PCI: CLS 0 bytes, default 64

[ 1.390478] ehci-pci: EHCI PCI platform driver

[ 1.406623] ohci-pci: OHCI PCI platform driver

[ 2.652819] imx6q-pcie 33800000.pcie: 33800000.pcie supply epdev_on not found, using dummy regulator

[ 2.662252] imx6q-pcie 33800000.pcie: PLL REF_CLK is used!.

[ 2.668456] imx6q-pcie 33800000.pcie: PCIe PHY PLL clock is locked.

[ 2.702156] imx6q-pcie 33800000.pcie: PCIe PLL locked after 0 us.

[ 2.708478] imx6q-pcie 33800000.pcie: host bridge /pcie@33800000 ranges:

[ 2.718820] imx6q-pcie 33800000.pcie: No bus range found for /pcie@33800000, using [bus 00-ff]

[ 2.731283] imx6q-pcie 33800000.pcie: IO 0x1ff80000..0x1ff8ffff -> 0x00000000

[ 2.742337] imx6q-pcie 33800000.pcie: MEM 0x18000000..0x1fefffff -> 0x18000000

[ 3.754072] imx6q-pcie 33800000.pcie: Phy link never came up

[ 3.760970] imx6q-pcie 33800000.pcie: failed to initialize host

[ 3.769652] imx6q-pcie 33800000.pcie: unable to add pcie port.

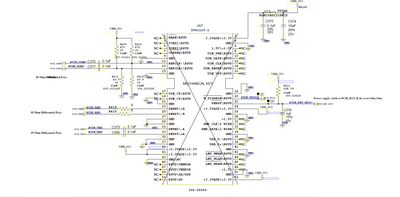

Also the schematic of PCI section is as below:

We are using internal clock, so taken reference from EVK PCIe nodes. With some modifications, below is the device tree node:

pinctrl_pcie: pciegrp {

fsl,pins = <

/* MX8MP_IOMUXC_I2C4_SCL__PCIE_CLKREQ_B 0x61 open drain, pull up */

MX8MP_IOMUXC_SAI1_MCLK__GPIO4_IO20 0x41

MX8MP_IOMUXC_SAI1_TXD6__GPIO4_IO18 0x41

>;

};

&pcie{

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_pcie>;

disable-gpio = <&gpio4 20 GPIO_ACTIVE_LOW>;

reset-gpio = <&gpio4 18 GPIO_ACTIVE_LOW>;

ext_osc = <0>;

clocks = <&clk IMX8MP_CLK_HSIO_AXI_DIV>,

<&clk IMX8MP_CLK_PCIE_AUX>,

<&clk IMX8MP_CLK_PCIE_PHY>,

<&clk IMX8MP_CLK_PCIE_ROOT>;

clock-names = "pcie", "pcie_aux", "pcie_phy", "pcie_bus";

assigned-clocks = <&clk IMX8MP_CLK_HSIO_AXI_SRC>,

<&clk IMX8MP_CLK_PCIE_AUX>;

assigned-clock-parents = <&clk IMX8MP_SYS_PLL2_500M>,

<&clk IMX8MP_SYS_PLL2_50M>;

status = "okay";

};

&pcie_phy{

ext_osc = <0>;

status = "okay";

};

&pcie_ep{

status = "disabled";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_pcie>;

ext_osc = <1>;

clocks = <&clk IMX8MP_CLK_HSIO_AXI_DIV>,

<&clk IMX8MP_CLK_PCIE_AUX>,

<&clk IMX8MP_CLK_PCIE_PHY>,

<&clk IMX8MP_CLK_PCIE_ROOT>;

clock-names = "pcie", "pcie_aux", "pcie_phy", "pcie_bus";

assigned-clocks = <&clk IMX8MP_CLK_HSIO_AXI_SRC>,

<&clk IMX8MP_CLK_PCIE_AUX>;

assigned-clock-parents = <&clk IMX8MP_SYS_PLL2_500M>,

<&clk IMX8MP_SYS_PLL2_50M>;

};

For now we are validating the hardware design as per the hardware design guide. Please help with some pointers on troubleshooting. Thanks in advance.

Regards,

Kunal

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kunal

one can look at below example with similar configuration, also recommended to try several pcie cards:

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @igorpadykov,

PCIe is working for us now. It was an issue with our h/w or the module. With another setup it is working. We can close this ticket now.

Thank you for your response.

Regards,

Kunal