- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

PCIE PLL lock time out on IMX7D?

Hi we are running the PCIE clock of the internal PLL and during boot we receive an error that the PCIE PLL lock has timed out. Both the 1.0V and 1.8V supplies have power. Is there something else to look for?

Hi Benjamin,

Are you able to get PCI working in Linux?

I don't see PCI support in U-Boot for mx7dsabresd.

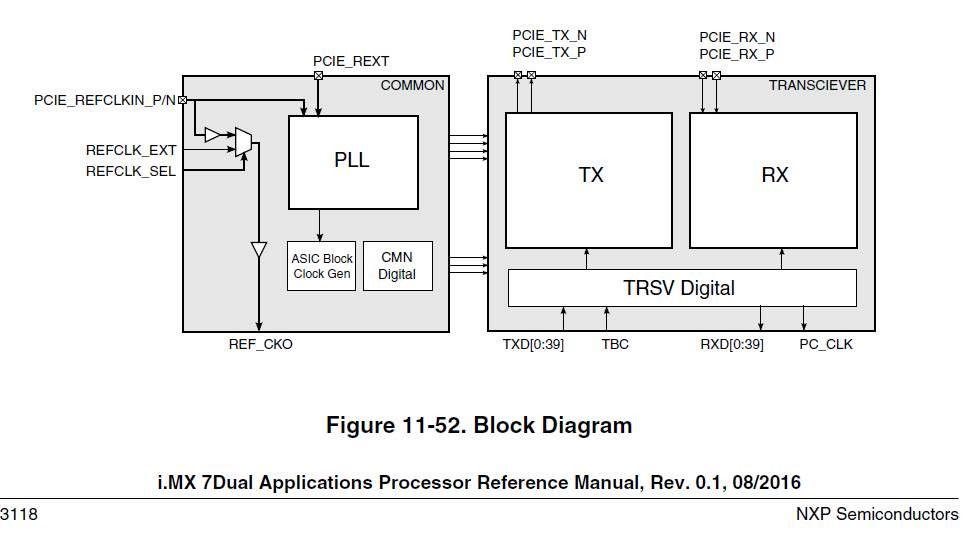

On the Sabre board we can lock the PCI Phy PLL using the external oscillator on the board, but if remove the 0 Ohm resistors to mimic our board and attempt to set the Phy to the internal 100 MHz we get same "unable to sync pll" error we see on our board. Figure 11-52 shown below suggests the PLL is only connected to the PCIE_REFCLKIN and that an external oscillator/clock IS required.

Thoughts?

Hello,

The current i.MX7 Datasheet contains misprints regarding PCIe PHY reference

clock requirements:

1. The min value of VMAX (33) and the min value of VMIN (400) should be removed.

2. The max value of VCROSS should be 550mV.

So, our PCIe PHY reference clock requirements is - at least - very close to HCSL.

Regards,

Yuri.

Hello,

hope the following helps.

https://community.nxp.com/message/918627

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Also to be clear, can the PCIe phy be run without an external clock on PCIE_REFCLKIN_P/N and only using the internal oscillator? Also is PCIE_REFCLKIN_P/N LVDS or HCSL compatible?

Hello,

You may look at "PCIe® Certification Guide for i.MX 7Dual", where we can see,

that the PCIE clock can be generated by the chip; no external clock is required.

https://www.nxp.com/docs/en/user-guide/PCIECGFIMX7DUG.pdf

Regards,

Yuri.

Testing on the MCIMX7D-SABRE board, if we remove the 0R R632 and R633, disconnecting the external oscillator from PCIE_REFCLKIN_N/P, what registers do we need to set to obtain a PLL lock of the internal oscillator for the PCI Phy?

Thanks

We tried this and it has not resolved the issue.