- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- PCI Express "phy never came up" with BSP 3.10.17_1.0.2-GA, custom board

PCI Express "phy never came up" with BSP 3.10.17_1.0.2-GA, custom board

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

PCI Express "phy never came up" with BSP 3.10.17_1.0.2-GA, custom board

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello everybody,

We have desisgned a custom board with the imx6 dual, where the pci express is used to connect an Exar PCI Express UART (XR17V358).

Out software is based on the Freescale Yocto BSP 3.10.17_1.0.2-GA.

On some boards there a startup problems where the pci express link is not always comming up ("phy never came up" in boot log).

Adding additional debug messages, are showing that the LTSSM stays in DETECT and POLLING states.

I have seen those other threads regarding pcie, but couldn't find a solution yet ( except from upgrading to a newer release, which we haven't tried yet).

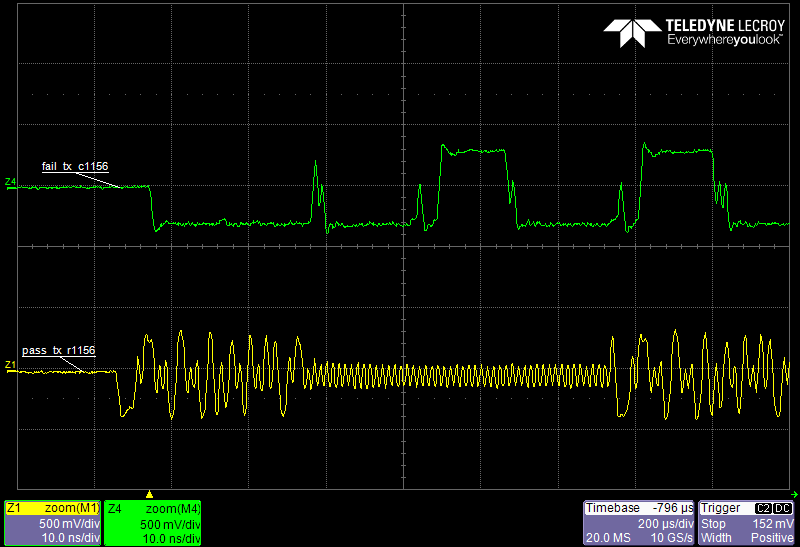

I've measured the pcie signals and could clearly see the difference between the cases where the link comes up and those where not.

In the cases it is working, all signals looked like valid PCIe signals (Z1, yellow), as far as I can tell with 600MHz bandwidth, when the link does not come up,

both tx signals are looking totally different ( Z4 green).

(There are two different measurements from two boot processes show, both on the same tx line, the reduced level of the high speed parts are probalbly related to the bandwidth of the scope).

As the signal is clearly broken, I don't think we are seeing signal problems that can be handeled by changing the IOMUXC_GPR8 register as mentioned here: AN4784

How often the error is happening, is related to the temperature:

One PCB that has the error in most cases at about 23 degree Celsius, starts successful cooled down with colling spray.

Another, after some fixes to the ldo bypass mode, starts successfully a room temperature but fails below 5 degree Celsius.

Other boards don't show any problems between 55 degree and -25 degree Celsius.

It seems also somehow related if the chips is powered in ldo bypass mode or in ldo mode.

This is, why my guess is, that the pcie phy is not comming up, may be because of unstable clocks.

What currently seems to improve the stability, is enabling the pcie_ref_125m clock very early with adding:

clk_prepare_enable(clk[pcie_ref_125m]);

to the end of imx6q_clocks_init().

Any hints, on how we might get this stabilized?

Regards, Jonas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jonas

difference in ldo bypass mode or in ldo mode may be handled

attached patches.

Regarding different behaviour from temperature: this may point to

weak signals, so tweakung IOMUXC_GPR8 may have sense.

Also this may point to 24MHz crystal instability, one can try to change it

from good boards.

Another test may be small lowering the core voltage of i.MX6.

Check that PCIe_EXT resistance is 200OHM 1% precision

and PCIE_VP/PCIE_VPTX connected to VDDSOC_CAP and good

filtered.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi igor,

I've also encountered this problem recently. My kernel is 3.10.53 from Android KK4.4.3_2.0.0。

I reviewd my kernel source, the driver/pci/host/pci-imx6.c already have been patched, but there is not arch/arm/cpu/armv7/mx6/soc.c in my kernel.

Coudle please help me,

Thanks!!!

John

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, The patch with arch/arm/cpu/armv7/mx6/soc.c is supposed to be used with u-boot. Regards, Jonas