- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Micrel KSZ9031 var-som-mx6 1GBps issue

Micrel KSZ9031 var-som-mx6 1GBps issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Micrel KSZ9031 var-som-mx6 1GBps issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

Its me again. I was developing ethernet driver for custom OS, so i am not using Linux. 100 MBps connection works fine but if we switch to 1000 MBps the data transmit through the line gets corrupted, however Auto-Negotiation successfully occurs and both the link partners switch to 1GBps connection but data transmission is not right. I am using 125-MHz clock (ENET_PLL-> div = 3) and setting SPEED bit in ECR_REGISTER to 1 for 1GBPs. I also set RGMII_CLOCK_SKEW to 0x3ff (as mentioned in U-Boot), if i leave clock skew register to it default value, no data transmit through the line. If i set it to 0x3ff data corruption is observed. I also set RX_SKEW to 0 and CONTROL_SKEW to 0 but still not help. Also went through micrel.c and net/FEC linux driver but still no luck. If any one plz could suggest if I am missing anything would be really helpful. Looking forward for you kind respnse.

Thanks,

Hamza.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

how about now,please

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Hamza

it may be useful to check timings with oscilloscope

given in sect.4.11.5.3 RGMII Signal Switching Specifications

i.MX6DQ Datasheet

http://cache.freescale.com/files/32bit/doc/data_sheet/IMX6DQCEC.pdf

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Your quick response is always appreciated. Unfortunately I don't have oscilloscope available with me, but after hacking code from u-boot I hope that my current PAD settings are good, please correct me if I am wrong:

RX Data Pad Skew = 0x0;

TX Data Pad Skew = 0x0;

Control Signal Pad Skew = 0x0;

Clock Pad Skew = 0x3ff;

Attached manual also says that DDR_SEL should be 0b11 and DSE should be 0b111, why we need to increase the voltage ? Although I tried it also but still can not transmit packets successfully.

I am also using CCM_ANALOG_PLL_ENET->divider = 3 which I am assuming that the clock would be 125 MHz. Also MII Speed divider I am using is 24 which should feed PHY clock of 2.5 MHz.

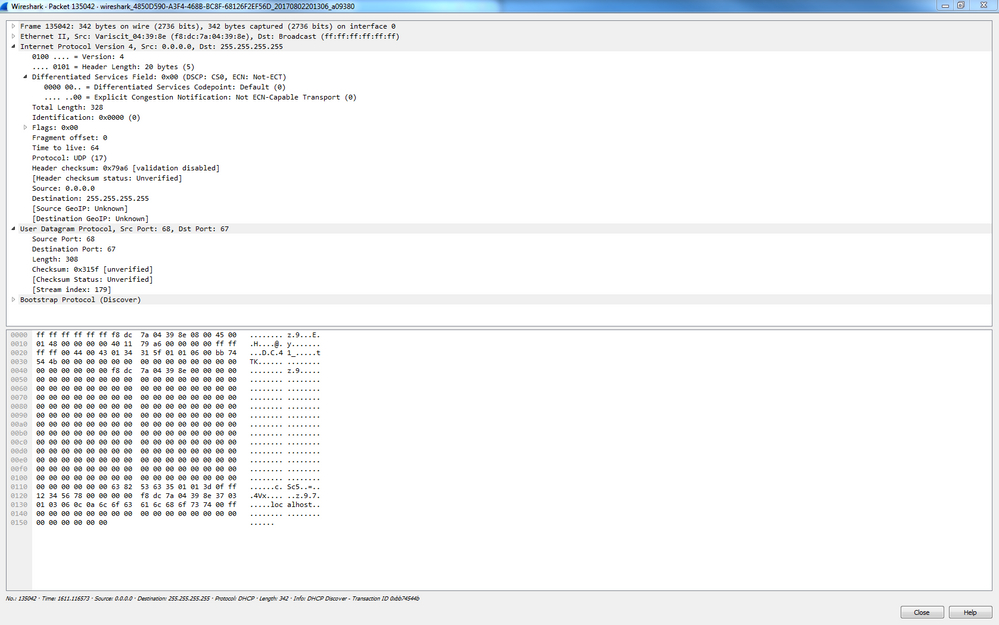

For clearing my problem a little more to you, I sent same DHCP Discover packet for both 100 Mbps and 1000 Mbps modes. 100 Mbps behavior was correct and packet looked like this on wireshark.

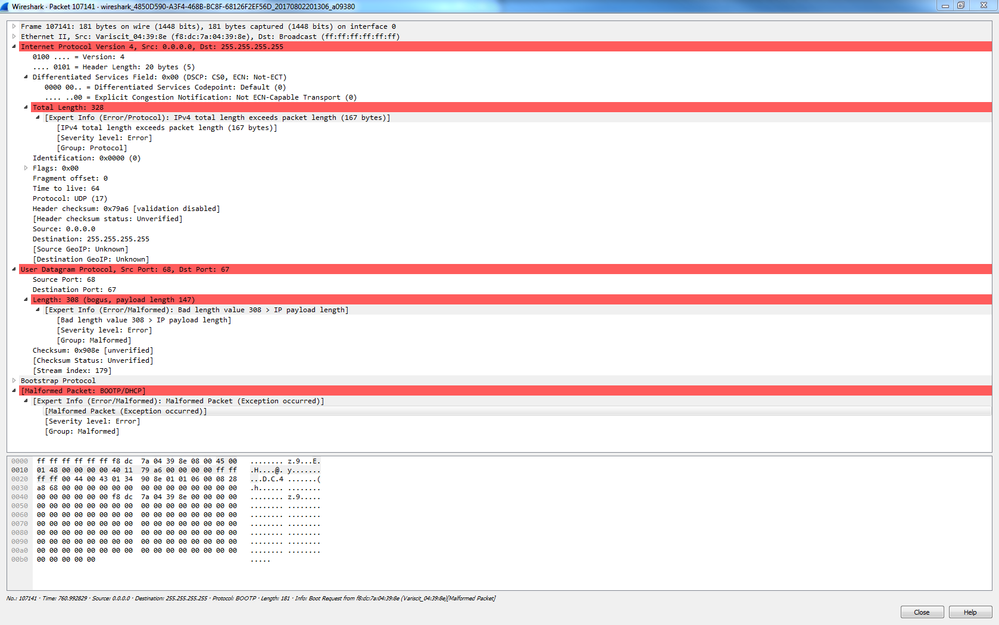

But when I transmit the same packet for 1000 Mbps the packet got corrupted and I got following log:

Since I don't have oscilloscope available with me it would be very nice of you to verify my skew values. also by looking at both the packets what you think can be a problem. Please ask me if I need to provide you more details. Yous help would be really highly appreciated :smileyhappy:

Thanks,

Hamza.