- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Meaning of "Pull Resistor Enable Field" at Config Tools for i.MX v9

Meaning of "Pull Resistor Enable Field" at Config Tools for i.MX v9

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Good Morning,

A simple question, at Config Tools for i.MX v9, one of the options to configure a GPIO is "Pull Resistor Enable Field", what is the exact meaning of this option ? Can you also verify if the other options I understand correctly (see below) ?

Pull-Up Enable Field - Include a Pull-up at internal PAD works for Input and Output.

Software Input on Field - Read the PAD in a Output GPIO, wors for Output only

Hysteresis Enable Field - Hysteresis the input signal, works for input only

Open Drain Enable Field - Open Drain Output, works for Output only

Slew rate Field - Output slew rate - works for Output only

Drive Strenght Field - Output Drive Strength - works for Output only

Thanks

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sergio

your understanding is correct except SION (Software Input on Field) - it works

for Input and Output. Also may be useful AN5078

Influence of Pin Setting on System Function and Performance

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sergio

your understanding is correct except SION (Software Input on Field) - it works

for Input and Output. Also may be useful AN5078

Influence of Pin Setting on System Function and Performance

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Igor,

Thanks for Quick answer.

How about the "Pull Resistor Enable Field" ? As the Pull-Up resistor is another field, what is the meaning of this "Pull Resistor Enable Field" ?

At the .c this option is the "PE:" as below:

- {pin_num: AB9, peripheral: GPIO1, signal: 'gpio_io, 15', pin_signal: GPIO1_IO15, PE: Disabled}

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

>How about the "Pull Resistor Enable Field" ?

your understanding is correct:

"Pull-Up Enable Field - Include a Pull-up at internal PAD works for Input and Output."

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Igor,

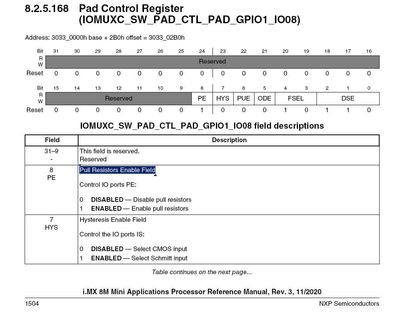

look the attached picture, there is two different fields

"Pull Resistors Enable Field"

"Pull Up Enable Field"

one generate in .c "PE: " and the other "PUE:" as below:

- {pin_num: AG10, peripheral: GPIO1, signal: 'gpio_io, 08', pin_signal: GPIO1_IO08, identifier: RTC_INT_N, direction: INPUT, PE: Enabled, PUE: Enabled, SION: DISABLED,

HYS: Enabled, FSEL: SLOW0, DSE: X1_0}

The Pull-up I understand, I wan't to understand what is the "Pull Resistors Enable Field"

Sérgio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

>I wan't to understand what is the "Pull Resistors Enable Field"

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Igor, thanks for the answer.

For me it is not clear yet... I had seen this table... let me try to explain.

Is this register a "global Pull configuration" ? Then if this register is disable the Pull-Up register next is don't care ?

Or it is a Pull-Down enable Register ? Or Other thing.... the sentence: "Pull Resistor Enable Field" is too vage

And it is valid for input or output ?.... I wan't to understand what is physically happen when I enable this register...

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

>Is this register a "global Pull configuration" ?

yes

>And it is valid for input or output ?

for both

Best regards

igor