- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: MDIO bus: MDC signal inverted on iMX8XL

MDIO bus: MDC signal inverted on iMX8XL

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MDIO bus: MDC signal inverted on iMX8XL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello!

I'm working with iMX8DXL BSP "imx-5.10.72-2.2.0".

I'm trying to get the ethernet up, but my phytter doesn't answer.

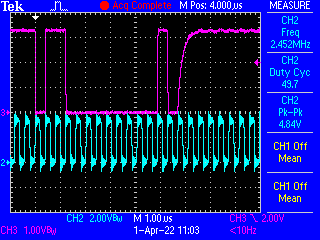

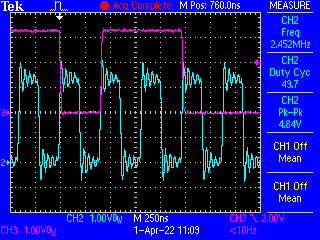

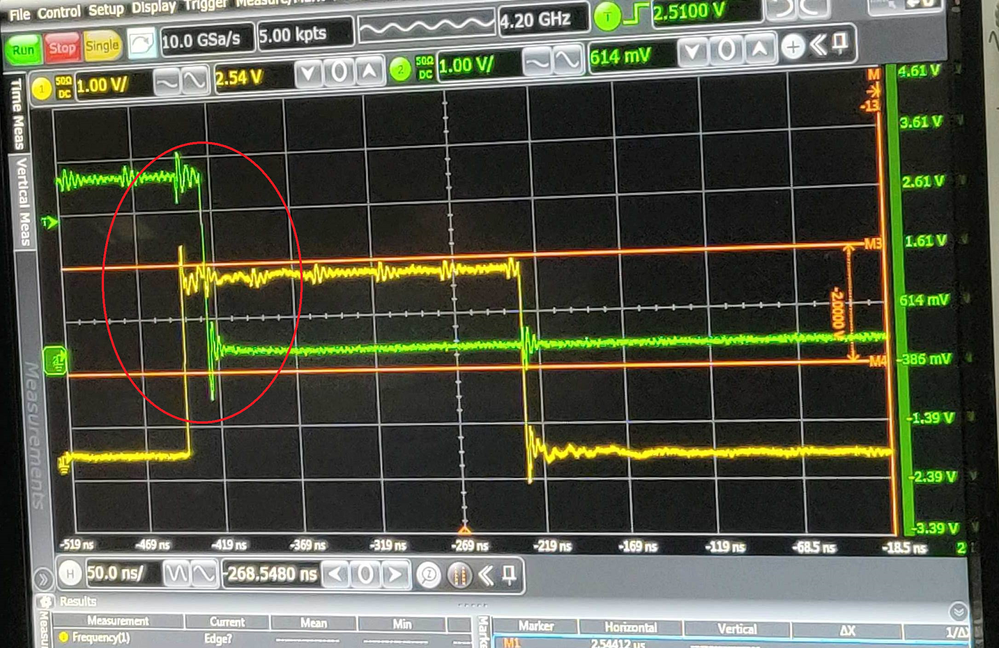

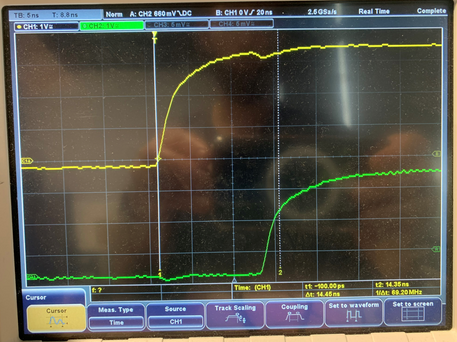

Using an oscilloscope I see the clock signal of MDIO bus (MDC) is inverted as expexcted.

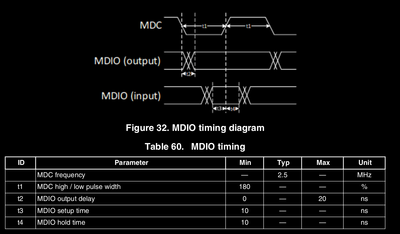

From datasheet:

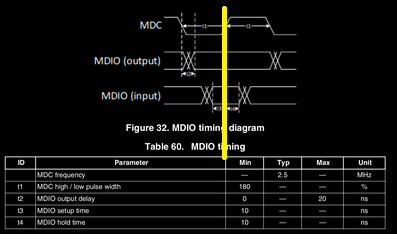

As you can see here, output data must change at the latest 20ns after MDC falling edge; it must be stable when rising edge occurs.

Reality is upside down. It seems to be synchronized with falling edge instead of rising edge.

Does anyone know a way to invert (by software) this signal? Or maybe using another mdio driver?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Because you osc is not fine enough to get the wave clearly.

The same is at "tail". It respects to the spec. It is about 15ns.

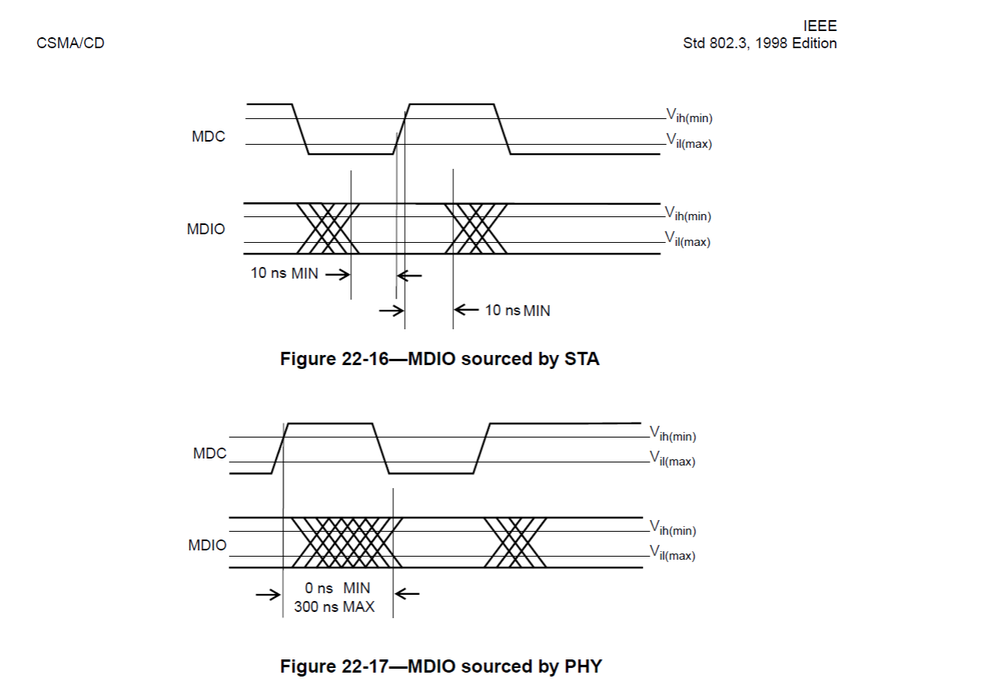

It respects to the spec 10ns, sourced by sta(input).

It is 20ns for soured by phy(output), respects to the spec 0 ~ 300ns.

BTW, spec never says failing edge, is somewhere else in spec?

Marked in yellow in your picture from datasheet.

MDIO (Management Data Input/Output) is a bidirectional signal that can be sourced by the Station Management

Entity (STA) or the PHY. When the STA sources the MDIO signal, the STA shall provide a minimum

of 10 ns of setup time and a minimum of 10 ns of hold time referenced to the rising edge of MDC, as shown

in figure 22-16, measured at the MII connector.

When the MDIO signal is sourced by the PHY, it is sampled by the STA synchronously with respect to the

rising edge of MDC. The clock to output delay from the PHY, as measured at the MII connector, shall be a

minimum of 0 ns, and a maximum of 300 ns, as shown in figure 22-17.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Setup time is about 12ns.

"BTW, spec never says failing edge, is somewhere else in spec? "

True, there is not written explanation, just "Each bit is transferred on the rising edge of the MDIO clock (MDC signal).".

I am based on the picture I attached from the iMX8DXL datasheet. There you can see that the timing of data change is related to the falling edge of the clock.

"2.10.4.3 MDIO" from IMX8DXLAEC_RevB.pdf; "4.10.5.3 MDIO" from IMX8DXLAEC_EMU_RevB.pdf