- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: LVDS - set Vsync and Hsync fixed to low

LVDS - set Vsync and Hsync fixed to low

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LVDS - set Vsync and Hsync fixed to low

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

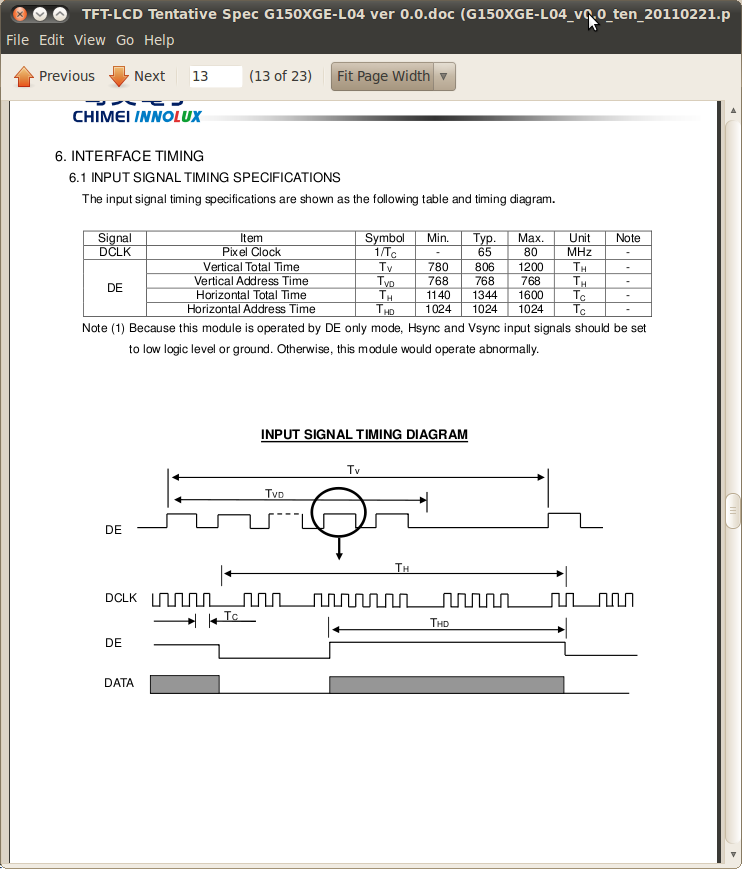

Unfortunately the display that my customer wants to drive specifically states that it requires Vsync & Hsync to be low, as opposed to the display that we use on the SDP which doesn’t even mention Vsync (VS) or Hsync (HS)

See page 16 of the attached datasheet and note 1

Instead of "blocking" the vsync/hsync signals from entering the LVDS block (which may not be possible), perhaps we can think of another work-around?

For example, if we could convince the IPU __not__ to generate any vsync/hsync waveforms, we'd be high and dry. The waveforms are set up in file ipu_disp.c, function ipu_init_sync_panel(). But !! The setup is very complicated, and I do not understand what it does, even when reading the relevant sections in the manual

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

jamesbone can you help to continue with the follow up of this case?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

One of our design partners has figured out how to do this within the i.MX6 so I'm assuming we can figure it out also, or maybe we just pay them to show us how to use our devices.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi John, if the customer doesn't need IPU to output the vsync and hsync to LVDS, they can mody the followed code in ipu_disp.c, function ipu_init_sync_panel():

From

/* Setup external (delayed) HSYNC waveform */

_ipu_di_sync_config(ipu, disp, DI_SYNC_HSYNC, h_total - 1,

DI_SYNC_CLK, div * v_to_h_sync, DI_SYNC_CLK,

0, DI_SYNC_NONE, 1, DI_SYNC_NONE,

DI_SYNC_CLK, 0, h_sync_width * 2);

/* Setup VSYNC waveform */

vsync_cnt = DI_SYNC_VSYNC;

_ipu_di_sync_config(ipu, disp, DI_SYNC_VSYNC, v_total - 1,

DI_SYNC_INT_HSYNC, 0, DI_SYNC_NONE, 0,

DI_SYNC_NONE, 1, DI_SYNC_NONE,

DI_SYNC_INT_HSYNC, 0, v_sync_width * 2);

To

/* Setup external (delayed) HSYNC waveform */

_ipu_di_sync_config(ipu, disp, DI_SYNC_HSYNC, h_total - 1,

DI_SYNC_CLK, div * v_to_h_sync, DI_SYNC_CLK,

0, DI_SYNC_NONE, 1, DI_SYNC_NONE,

DI_SYNC_NONE, 0, 0);

/* Setup VSYNC waveform */

vsync_cnt = DI_SYNC_VSYNC;

_ipu_di_sync_config(ipu, disp, DI_SYNC_VSYNC, v_total - 1,

DI_SYNC_INT_HSYNC, 0, DI_SYNC_NONE, 0,

DI_SYNC_NONE, 1, DI_SYNC_NONE,

DI_SYNC_NONE, 0, 0);

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Qiang_FSL

Thanks for your answer. After applying the changes you suggested the customer is reporting that not even the TX_CLK0 signal is being generated and he is getting an floating point exception on the OS initialization.

Any ideas what could be wrong ?

Cheers,

Marco

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

It seems the VSYNC and HSYNC is must in LDB side to convert the display signal to LVDS serial signal.

Another thing can be tried is to switch the low/high active for HSYNC and VSYNC, the original seting is low active:

{

"LDB-XGA", 60, 1024, 768, 15385,

220, 40,

21, 7,

60, 10,

0,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,},

Customer can try:

{

"LDB-XGA", 60, 1024, 768, 15385,

220, 40,

21, 7,

60, 10,

FB_SYNC_HOR_HIGH_ACT | FB_SYNC_VERT_HIGH_ACT,

FB_VMODE_NONINTERLACED,

FB_MODE_IS_DETAILED,},

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Qiang Li,

Thanks for your suggestion. This had the impact that the VSYNC and HSYNC Signals were reduced but not completely deactivated them.

We need a solution to set both signals "permanently" to LOW.

Do you have another idea how to implement it?

Cheers,

Marco

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Marco, there is no solution to set both signals "permanently" to LOW for LVDS panel. In iMX6 internal, the IPU display interface will output parallel video data to LVDS module, then LVDS module will convert this parallel input to LVDS serial signal and output from LVDS port, for such convert, VSYNC and HSYNC is needed, so IPU DI must output valid VSYNC and HSYNC to LVDS, and the LVDS bridge will always fill the HSYNC and VSYNC data into LVDS package.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

FYI, one of our design partners has it working with the i.MX6, but they are not going to give us the solution because they had to devote resources to make it work, so there’s obviously a way to do it.

John

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi John, if the customer used parallel panel, the use case can be supported, but for LVDS panel, it can't.

By the way, from LVDS panel side, when converting the LVDS signal to parallel RGB signal, maybe the customer can disconnect the HSYNC and VSYNC pins.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

jamesbone any update here?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Qiang_FSL are you able to help here?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have also a lcd display with DE only mode, and i can't set hsync and vsync to low, when I set hsync_len and vsync_len to zero in ldb.c i have a error when boot my board.

Is that someone have a solution ?

this is the timing of my lcd :

Fabien.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

So, did you just add a new data inside ldb_modedb[] struct in ldb.c? how did you compute for the pixclock? did you just set hsync_len and vsync_len to zero then, since they are being ignored in DE mode?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have calculated the pixel clock manually. But you will also find some macros in this forum: Linux Framebuffer driver: Calculate Pixel Clock for struct fb_videomode -blog archive

VSync and HSync pulse width is not set to zero as I think this is not valid configuration. In my case these signales are discareded automatically by the LVDS converter on my display. So only DE signale is connected to the LCD display. My first proposal therefore was not correct that it is required to set these signales to fixed low.

Do you have comparable problems with LVDS disaplay?

In my cause the problem was cause by an invalid pixel clock. Unfortunatly the default PLL used in LVDS driver is to fast to achieve clocks below 40MHz. Therefor I needed to select another PLL for lower display clocks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

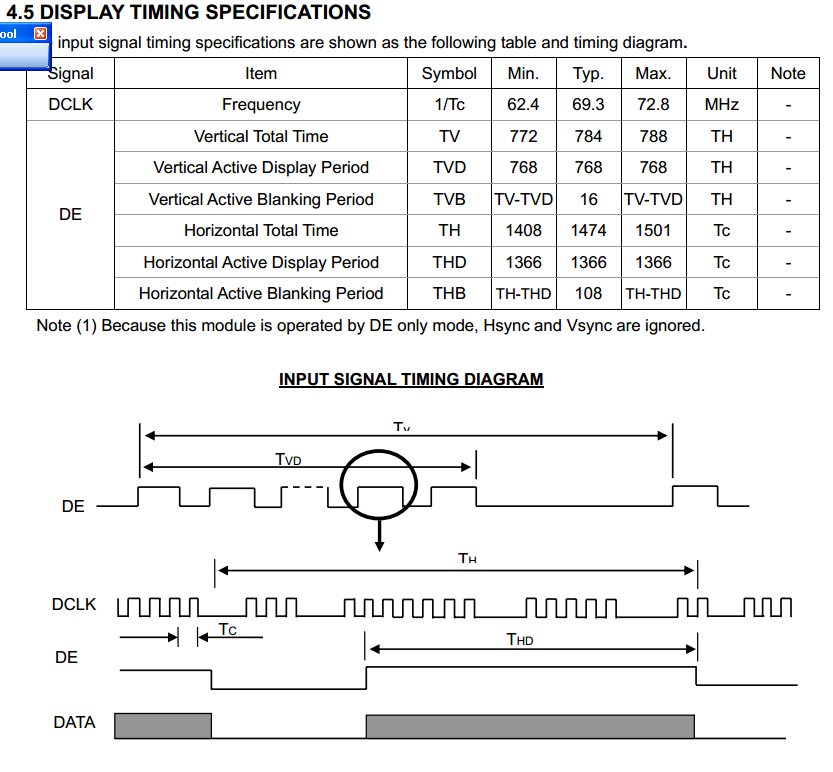

Basically I'm having trouble dealing with the timings and stuff. Here is the datasheet for my lvds lcd.

Now since my lvds is in DE mode only, it also disregards hsync_len and vsync_len. and since there seems to be no mention of hsync or vsync, I thought I should set them to zero as well. That leaves my calculation of pixclock to have hsync and vsync to be zero since both are part of the function to get pixclock. I just haven't tested the "zero hsync and vsync" since the lcd haven't arrived yet, but as you mentioned, a zero configuration seems an invalid configuration so I am lost now what to put as vsync_len and hsync_len...

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Check the IOMUX options for these pins. If they can be configured in GPIO mode, then you could put them in zero.

Regards,

Fabio Estevam

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I did not find any setting in the IOMUX section to control this, even in the GPRs.

The VSYNC signal from IPU to LVDS Bridge (ipu_di0_vsync) is internally only. So in my understanding the only location to adjust this might be in the LDB.

Meanwhile I have detected that this wasn't the reason for my problem. The LVDS circuit on the Display itself discards the sync signales (and uses DE only). Hence I think that the option I was searching for will never be required!

Thanks for your post anyway.