- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- LVDS Display Configuration (timing+clock)

LVDS Display Configuration (timing+clock)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LVDS Display Configuration (timing+clock)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have an IMX6 board with an LVDS display attached (split-mode).

I configured the mxcfb in this way:

mxcfb1: fb@0 {

compatible = "fsl,mxc_sdc_fb";

disp_dev = "ldb";

interface_pix_fmt = "RGB24";

mode_str ="LVDS-WUXGA";

default_bpp = <32>;

int_clk = <0>;

late_init = <0>;

status = "disabled";

And the timing in this way:

lvds-channel@0 {

reg = <0>;

fsl,data-mapping = "spwg"; /* "jeida"; */

fsl,data-width = <24>;

crtc = "ipu2-di1";

primary;

status = "okay";

display-timings {....

timing_wuxga: LVDS-WUXGA {

clock-frequency = <149992500>;

hactive = <1920>;

hback-porch = <20>;

hfront-porch = <100>;

hsync-len = <18>;

hsync-active = <0>;

vactive = <1200>;

vback-porch = <4>;

vfront-porch = <6>;

vsync-len = <2>;

vsync-active = <0>;

de-active = <1>;

pixelclk-active = <0>;};

Now, if I start the kernel with parameter in uboot like:

video=mxcfb0:dev=ldb,1920x1200M@60,if=RGB24,bpp=32 ..

The image start with an high clock (like ~190MHz), this because it use the VESA CVT formula.

It obviously is out of clock, with bad timing etc.., but with the fbset command:

/usr/sbin/fbset -g 1920 1200 1920 1200 32 -vsync 0 -t 6667 20 100 4 6 18 2

I get a perfect image.

Point: until the device is not started, and the fbset executed I get a bad image, but after executing this command everything is configured correctly.

If i remove the uboot param:

video=mxcfb0:dev=ldb,1920x1200M@60,if=RGB24,bpp=32 ..

The default parameter is taken from device tree, I get the correct fbset configuration:

mode "1920x1200-60"

# D: 149.993 MHz, H: 72.883 kHz, V: 60.134 Hz

geometry 1920 1200 1920 2400 32

timings 6667 20 100 4 6 18 2

rgba 8/16,8/8,8/0,8/24

endmode

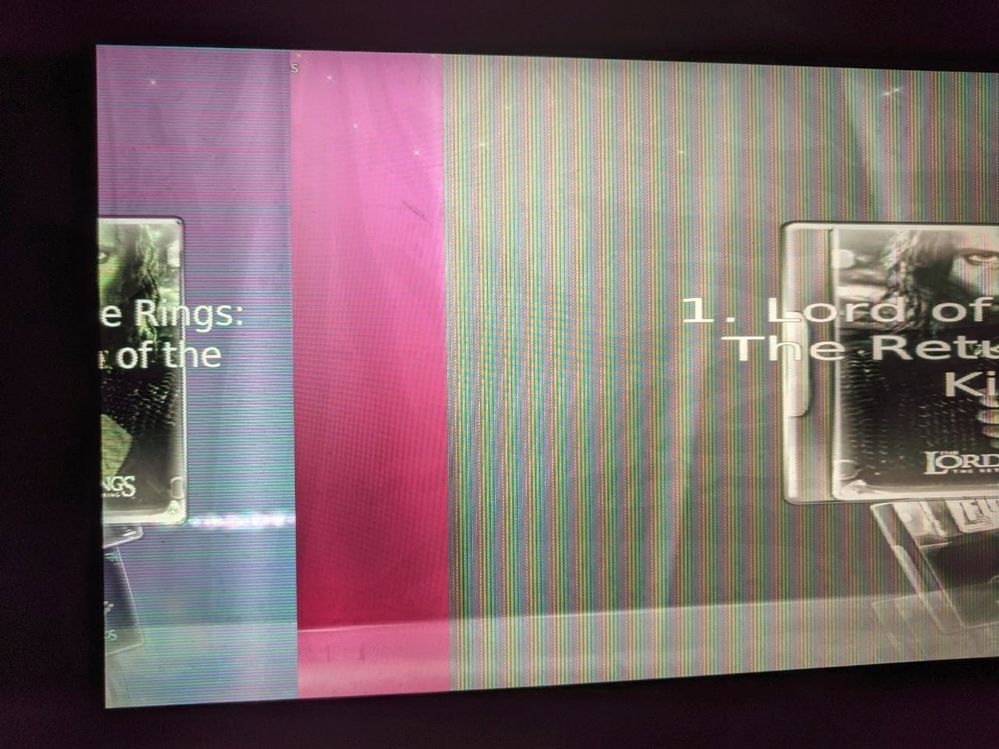

But the image is not good (see attached image).

Executing fbset command in this case doesn't change anything, the image is bad.

I think that is a clock problem or something like this, the timing correct.

Question: What the VESA CVT formula change other than timing and resolution? How I can set it in devicetree or in uboot? There is some clock change that I can made?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Cristian

One LVDS Channel can only support Max 1366x768(760) resolution.

Dual LVDS channle support max 1920x1080.

So LVDS doesn't support 1920x1200 resolution.

Hope above information is helpful to you.

Have great day!

B.R,

Weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank's for reply weidong.sun ,

as I said I configured it in split-mode, so I'm using two LVDS channels with one display.

Anyway if I start it with u-boot parameter

video=mxcfb0:dev=ldb,1920x1200M@60,if=RGB24,bpp=32

it start calculating timing with VESA CVT formula, and I get a bad timing and bad clock, but configuring it with fbset after start-up it work good.

So the Display working perfectly, but I need to start it with a VESA CVT mode, and then changing it after startup.

But seems very nasty, I would start it with the right configuration from boot.

But using the parameter in the DTS, all timing is correct (see fbset output), but the image is bad (see image in the post).

There is something in the VESA calculation that will fix something.. but what?

What I miss to configure in my dts?

Clock base? ...?