- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

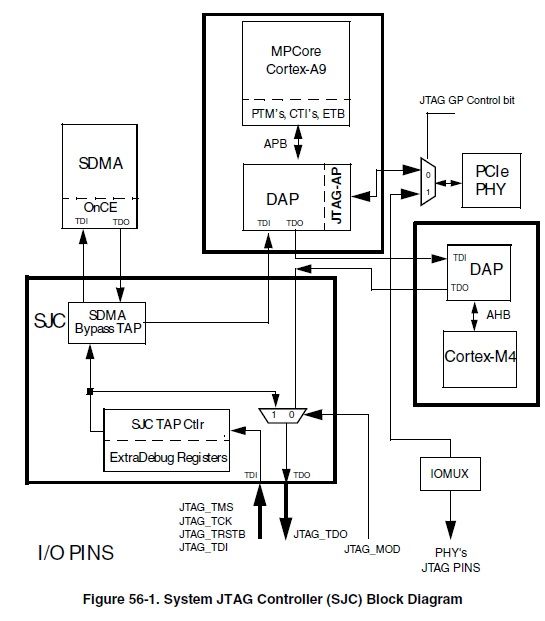

Is the DAP which enable to read CPU registers during JTAG debug session ?

Hi all,

I need some precision about JTAG scan chain.

I'm misunderstanding what is the device which halt/run the CPU during a JTAG debug session.

For example when I connect a JTAG debug tool to the JTAG pins, which device on the JTAG daisy-chain enable to read the CPU registers or halt it ?

In the document IMX6SDLRM, Rev. 2, 04/2014:

http://cache.nxp.com/files/32bit/doc/ref_manual/IMX6SDLRM.pdf?fsrch=1&sr=1&pageNum=1

It is explaned (p. 364/5829):

"The SJC module is the bridge between external development and test instrumentation and

the internal JTAG-accessible debug and test resources."

An overview of the JTAG architecture is given(p. 4914/5829)

On the JTAG daisy-chain there are in particular 2 devices :

- The OnCE (On chip Emulator) of the SDMA

- The DAP (Debug Acces Port)

It is explained (p.366/5829) :

"The SDMA debug features are primarily defined by the OnCE portion of its design."

Please, I need some precision:

[Q1] Does the OnCE portion is used for debugging only the SDMA 32-bit RISC processor ?

[Q2] If I want to halt Cortex-A9 core, read its registers this is the DAP module which work on the JTAG chain ?

Thank you for any help.

Fabien.

Hi Fabien

[Q1] Does the OnCE portion is used for debugging only the SDMA 32-bit RISC processor ? :

Yes, OnCE is unrelated if you are trying to debug Cortex-A9 core.

[Q2] If I want to halt Cortex-A9 core, read its registers this is the DAP module which work on the JTAG chain ? :

Correct.

To give you an idea, here is the jtag chain description for iMX6Q we use with

our debugger (BDI3000 from Abatron) :

#0 SCANPRED 2 9 ;count for SJC and SDMA

#0 SCANSUCC 0 0 ;no device after DAP

Which tells our debugger to skip the first 2 devices in

the scan chain with a IR length of 9. Your JTAG

debugger might have a different way to describe the

DAP in the chain.

Hope this helps

Regards

Sinan Akman