- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- IMX6sx failed to boot from S25FL064L

IMX6sx failed to boot from S25FL064L

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IMX6sx failed to boot from S25FL064L

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have an issue with imx6sx boting with S25FL064L (use quad io).

0a1804eb # lut[0] command sequence

0e081200 # lut[1] command sequence

24001e04 # lut[2] command sequence

Verified the norflash chip registers are as expected

read control register 1: 0x02

read control register 2: 0x00

read control register 3: 0x78

read status register 1: 0x02

After power cycle, I have a BE/LE issue.

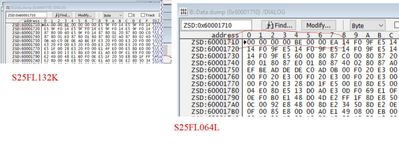

I have boards, left is a board with S25FL132K, which is working properly; right side is the same board just replaced S25FL132K with S25FL064L. Same u-boot is loaded.

The QSPI is not configured properly, the ENG_CFG should be 0 if configured properly

The lut vlaue is loaded properly

If I manually load u-boot-spl and u-boot, they both work fine.

The problem is bootrom does not load the u-boot to ram, and not execute it.

Not sure what is broken in the boot sequence. Any suggestion is apprecaited.

Thanks,

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jim

reason may be is that qspi configuration parameters were not updated for new qspi-nor,

described in Table 8-26. QuadSPI configuration parameters

i.MX 6SoloX Applications Processor Reference Manual

One can try to reprogram it using for example mfg tool (script mfgtool2-yocto-mx-sabresd-qspi-nor-n25q256a.vbs, samples: qspi-nor-macronix-mx25l51245g-config, qspi-nor-micron-n25q256a-config

in folder ./files) , prepare new config file for S25FL064L

or with new uuu tool: https://github.com/NXPmicro/mfgtools

sample script example_spinor.uuu can be found in Demo Images

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Igor:

Thank you very much for the reply!

I have sample config for S25FL132K, and it is working on the old board. I used all those samples and figured out a new config. I uploaded it here with datasheet

Control Register 1: (Quad IO mode is enabled properly)

Control reister 2: (3-byte register mode is set)

Control register 3: (dummy cycle is 8 cycles)

Status Register 1: (write enable latch is set)

These are the right setting I need from the device.

The SEQID0 command to setup QSPI, which matches the s25fl064l datasheet:

0a1804eb | enable quad io read, 3 bytes address will be sent in 4 pads |

0e081200 | dummy cycle is 8 cycles, and mode uses 1 pad |

24001e04 | Read 4 bytes |

The only instruction i am not sure is 1200. I was thinking it should be 0x1202: setting mode cycle to 2; but example tells set the number of pad for mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

so can you confirm that you flashed qspi-nor with modified qspi-nor-spansion-s25fl064l-config.txt

using mfg tool?

One can write them manually from uboot, for example load them to 0x80800000, then

write to qspi-nor from 0x400 offset:

sf write 0x80800000 0x400 0x200

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

U-Boot 2015.07-g2e0d69a-dirty (Feb 19 2021 - 08:16:12 -0600)

CPU: Freescale i.MX6SX rev1.3 at 792MHz

Reset cause: POR

Board: xxx

I2C: ready

DRAM: 512 MiB

WARNING: Caches not enabled

PMIC: PFUZE100 ID=0x11

MMC: FSL_SDHC: 0

*** Warning - bad CRC, using default environment

In: serial

Out: serial

Err: serial

Net: FEC0 [PRIME]

Hit any key to stop autoboot: 0

=> sf probe

SF: Got idcodes

00000000: 01 60 17 ff .`..

SF: Detected S25FL064L with page size 256 Bytes, erase size 64 KiB, total 8 MiB

device 0 offset 0x400, size 0x400

SF: 1024 bytes @ 0x400 Read: OK

=> md 0x80800000

80800000: 00000000 00000000 00000000 00000000 ................

80800010: 00000001 00000202 03000003 02000000 ................

80800020: 00000003 00000003 00800000 00000000 ................

80800030: 00000000 00000000 00000001 00000000 ................

80800040: 00000004 00000000 00000000 00000000 ................

80800050: 00000000 00000000 00000000 00000000 ................

80800060: 00000000 00000000 0a1804eb 0e081200

80800070: 24001e04 00000000 1c010405 00002400

80800080: 00000000 00000000 24000406 00000000 ........

80800090: 00000000 00000000 20010401 00002400 .......

808000a0: 00000000 00000000 00000000 00000000 ................

808000b0: 00000000 00000000 00000000 00000000 ................

808000c0: 00000000 00000000 00000000 00000000 ................

808000d0: 00000000 00000000 00000000 00000000 ................

808000e0: 00000000 00000000 00000000 00000000

808000f0: 00000000 00000000 00000000 00000000

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

one can try with image generated for S25FL132K, seems it is the same except nor size.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

igor:

If the norflash content can be viewed correctly from qspi mapped address 0x60000000, it means the qspi configuration is correct, right?

How would bootrom interact with norchip ? In what mode (single/dual/quad) it copies qspi configuration from 0x400 of the norchip? How does bootrom know what mode the chip is set ?

Thanks

Jim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jim

in general one can check non-volatile registers described on p.35

S25FL064L_64-Mbit_8-Mbyte_3.0_V_FL-L_SPI_Flash_Mem-1102570.pdf,

like QPI, Address Length at Power-up, e.t.c.

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Those info is provided in the initial post. After power cycle, the non volatile registers are as fellows:

read control register 1: 0x02 (quad mode)

read control register 2: 0x00 (3-byte address)

read control register 3: 0x78 (8 dummy cycle)

read status register 1: 0x02 (write latch enabled)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Flashed working image for S25FL132k to the new board, and it failed the exact same way:

1: QSPI MCR has wrong endiness

2: Reading norflash config/content from qspi mapped address 0x60001710, norflash content is correct.

Board still does not boot up itself.