- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Ethernet chip KSZ8081RNB not working with i.MX6UL

Hi,

We are trying to configure the KSZ8081RNB ethernet chip over management signals MDC and MDIO.

Clock quality is similar to evaluation board, however when CPU is trying to read the address, each time PHY chip is returning different address. This is not happening in Evaluation board. Clock frequency 2.35MHz.

Can anyone help us on this issue.

Regards,

Surendra

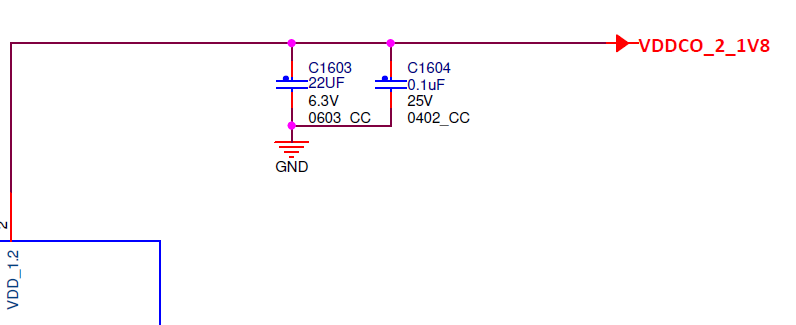

Here I want to add pne more thing that EVK board has used external 1.8V to drive reference power pin of PHY.

However we have not used external one.

Will it make any impact.

Regards,

Surendra.

Hi Surendra,

I feel the external pin is for powering up of the chip, if so, the device tree will have the entry of the pin doing so.

In your present case, have you taken care of the pin settings in Device tree?

It will be more helpful, if you could attach both the device tree files here.

Thanks,

Ramya

Hi Ramya,

However datasheet mantions that this reference pin must not be powered. Still EVK has connected it.

What do you mean by by device tree?

Do you see some other issue by which we are not getting proper data on MDIO pin.+

Regards,

Surendra

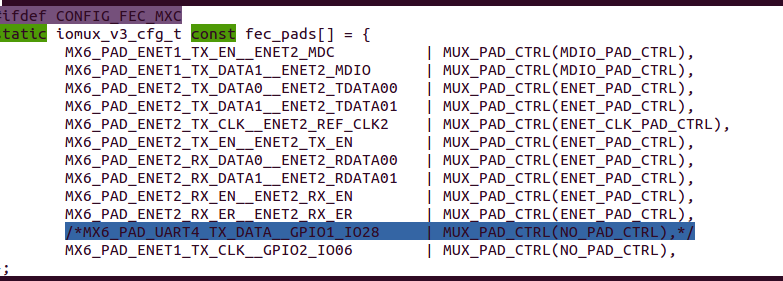

Hi,

We are testing ethernet in uBoot. We are not doing in Kernel.

Above fig. explains the pin muxing of Ethenet signals.

Regards,

Surendra

Hi Surendra,

Could you please tell me the uboot version, you are working with?

Also, which datasheet mentioned the pin should not be connected?

Thanks,

Ramya