- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- Re: EIM timing definition

EIM timing definition

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Community,

We are developing custom board with i.MX6D. However, we can not clearly understand specification of EIM timing parameters.

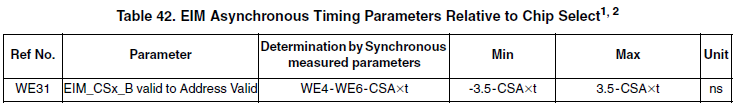

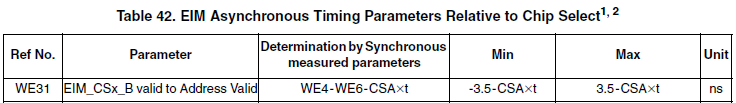

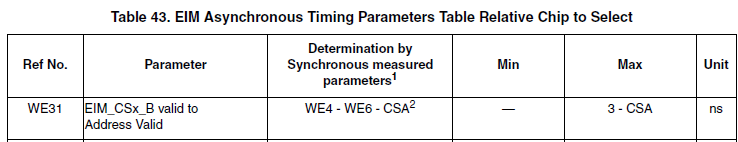

From IMX6DQAEC REV.5

Linux BSP implementation:

AXI_CLK_ROOT = 198MHz = PLL2 PFD2 396MHz / 2

ACLK_EIM_SLOW_CLK_ROOT = 99MHz = AXI_CLK_ROOT / 2

Questions:

Q1.

The datasheet is described that "t means clock period from axi_clk frequency".

In above case, should we use AXI_CLK_ROOT(198MHz) for "clock period for t"?

I suppose we should use ACLK_EIM_SLOW_CLK_ROOT(99MHz) instead of AXI_CLK_ROOT(198MHz). Is it right?

Q2.

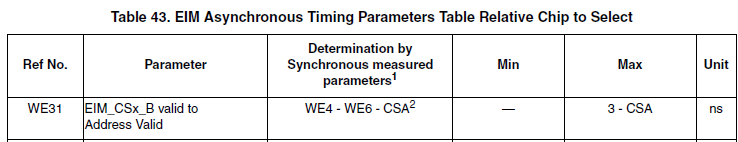

From IMX6SDLAEC REV.8

EIM timing definitions are different between i.MX6S/DL and i.MX6D/Q/DP/QP such as above figures.

I suppose i.MX6S and i.MX6D are using same EIM controller. but, why timing definitions are different as above?

Best Regards,

Kazuma Sasaki.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kazuma

1.> I suppose we should use ACLK_EIM_SLOW_CLK_ROOT(99MHz) instead of AXI_CLK_ROOT(198MHz). Is it right?

right

2. >why timing definitions are different as above?

timings are the same, first makes more sense as according to

EIM EIM_CSnRCR1 definition CSA is EIM clock cycles, so "unit" is given

as combination "t"&CSA.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kazuma

1.> I suppose we should use ACLK_EIM_SLOW_CLK_ROOT(99MHz) instead of AXI_CLK_ROOT(198MHz). Is it right?

right

2. >why timing definitions are different as above?

timings are the same, first makes more sense as according to

EIM EIM_CSnRCR1 definition CSA is EIM clock cycles, so "unit" is given

as combination "t"&CSA.

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi igor,

I appreciate your support. Let me confirm regarding Q2.

<Conditions>

(1) CSA = 1 cycle

(2) ACLK_EIM_SLOW_CLK_ROOT = 99MHz = 10.1 ns time per cycle

(3) Timing definition

From IMX6DQAEC REV.5

From IMX6SDLAEC REV.8

<Calculation>

In case of i.MX6D : WE31 MAX = 3.5 - CSA x t = 3.5 - 10.1 = -6.6ns

In case of i.MX6S : WE31 MAX = 3 - CSA = 3 - 10.1 = -7.1ns

<Question>

Is the above calculation correct? If correct, why timings are same in above case?

Best Regards,

Kazuma Sasaki.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kazuma

I think calculations are correct.

Where did you see that timings are same ?

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi igor,

I might not have understood that your first answer correctly.

You told me that "timings are the same" at your first answer on this thread.

I am worried about typo for EIM timing which described on datasheet.

Best Regards,

Kazuma Sasaki.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kazuma

if you mean WE31, they are not the same.

Best regards

igor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Igor,

I got it. thank you so much for your support.

Best Regards,

Kazuma Sasaki.