- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Typically, if no more than 4 memory chips is used and the PCB traces impedance is matched to 50 Ohm for single-ended signals and to 100 Ohm for differential pairs, the VTT termination is not required even when using the fly-by topology. In other case, the only way to fix the possible DDR bus issues is to redesign the PCB layout to add the VTT termination circuit.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Artur,

Thanks for the reply.

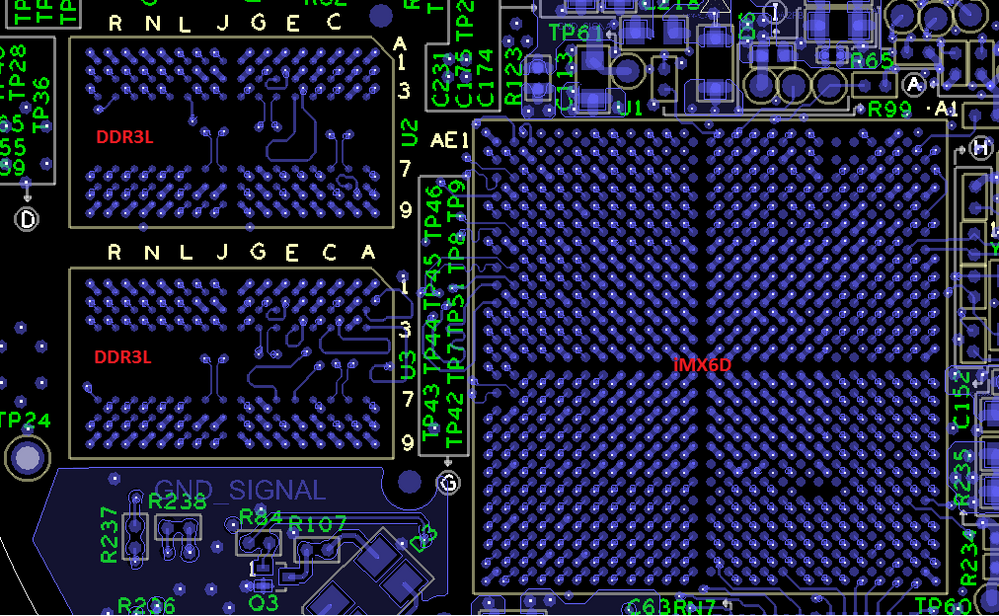

I have used 2 x DDR3L - 16 bit (Total system 32 bit) with Fly-by topology. And both are on TOP side only.

Please see attached image for your reference.

It means that my design will work without any issue though I don't kept bus termination resistors.

The fabrication of oard is done and it is in assembly preocess.

Regards,

Mrudang

Hi Artur,

Thanks for reply.

Parallally I am working on similar board which has iMX6Q with 4 x DDR3L (MT41K512M16HA-125:A) (Total density = 4GB).

- Can you please suggest me which is the right topology to rout DDR3L?

- Since I am using 4 DDR3L do I need to provide bus termination resistor support?

Provide me your valuable answer.

Regards,

Mrudang

1. The preferred topology for 4 memory chips with i.MX6 series processors is T-type. Please follow the design of the i.MX6 SABRE SD board.

2. No VTT termination is required in case of 4 memory chips with T topology routing.

Best Regards,

Artur

Hi Artur

I'm designing a board which can contain i.MX6 Quad, i.MX6 duallite and i.MX6 Solo in the same PCB.

When using Quad, we'll put 4 x DDR3L (MT41K512M16HA-125:A) (Total density = 4GB).

When using duallite we'll put 2 x DDR3L (MT41K512M16HA-125:A) (Total density = 2GB). making other 2 DDR3L no mount.

When using Solo we'll put 1 x DDR3L (MT41K512M16HA-125:A) (Total density = 1GB). making other 3 DDR3L no mount.

My doubt is that if I go with balanced T topology, will there be noise due to the stubs which will be there in the absence of 3 DDR3L RAMs (As in i.MX6 Solo configuration, the PCB remains same and only 1 DDR is populated)?

Or should I go with Flyby topology keeping all four RAMs on top layer?

You are right in that populating only one DDR chip on balanced T-topology bus may affect the signal integrity due to signal reflection on unused trace stubs. In this case, actually, the Fly-by topology seems to be more appropriate.

Best Regards,

Artur